Ok, sei stato molto chiaro, credo di aver preso tutto. Per ora non ho da aggiungere niente. Anche se sono un po' monotono, ti ringrazio ancora Isidoro!

[quote="Gost91"]dalla quale si capisce che il punto critico del sistema è il primo registro, nel senso che se il primo registro funziona allora anche il secondo registro funziona.

La conclusione e` corretta ma il ragionamento no.

TEOREMA (*): tutti i componenti (FF inclusi) sono miopi come talpe: non vedono 1mm oltre i proprii piedini!

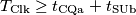

Il primo stadio lo sai analizzare, e` il divisore per due che funziona se Tclk>tCQ+tsu. Questa relazione dipende dal fatto che lui si genera il suo stesso ingresso. Il primo FF non sa da dove arriva il suo clock.

Il secondo FF e` esattamente nella stessa situazione: non sa da dove gli arriva il clock, e lui genera il suo stesso dato in ingresso. Il secondo stadio e` identico al primo, e quindi anche per lui la corretta temporizzazione richiede che Tclk>tCQ+tsu. E cosi` via per tutti gli eventuali altri stadi successivi.

Lo stadio piu` critico e` il primo, perche' e` quello che funziona con frequenza massima e quindi periodo di clock minimo. Il secondo stadio lavora a frequenza meta`, cioe` con periodo di clock doppio rispetto al primo.

Anche qui bisogna verificare che la durata degli impulsi sia maggiore di quella minima, specie per il primo stadio.

Proviamo a fare un conto usando questo FF. Supponiamo di lavorare a 25C di temperatura e 6V di alimentazione.

Il ritardo massimo di propagazione dal clock all'uscita vale in queste condizioni 30ns (pagina 7, si chiama tpd). Il tempo di set up vale 17ns (pagina 6, verso il fondo), quindi il periodo di clock deve essere maggiore di 47ns, che fa una frequenza minore o uguale di 21MHz.

MA c'e` anche da rispettare la limitazione sulla durata minima degli impulsi. Ad esempio posso usare un clock che sta per 24ns a livello basso e 24ns a livello alto, mentre non posso usare un segale di clock che sta 10ns a livello alto e 40ns a livello basso. In quest'ultimo caso il periodo totale e` di 50ns, quindi soddisfo Tclk, ma non soddisfo il parametro tw (meta` pagina 6), che deve essere di almeno 14ns.

Il secondo FF (e gli eventuali successivi) non ha piu` di questi problemi perche' sia il livello alto che quello basso hanno la stessa durata.

(*) preso dal mio prof di elettronica e adattato all'occorrenza!

[quote="Gost91"]

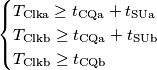

Per il primo registro le condizioni da rispettare sono:

Per il primo registro le condizioni da rispettare sono:

Per il primo FF non ci sono condizioni da rispettare. Il segnale di ingresso arriva in modo asincrono, non e` sotto il tuo controllo. E anche la seconda condizione che hai scritto non ha senso. La SOLA condizione da rispettare per il primo FF e` di avere il periodo di clock maggiore del periodo minimo di clock che viene dichiarato dal costruttore del FF e anche la parte alta e quella bassa dell'impulso devono essere piu` lunghe di un valore minimo sempre specificato dal costruttore.

Se poi il segnale di ingresso cambia troppo vicino al fronte attivo del clock, il FF puo` andare in metastabilita`, ma questo e` una cosa che il progettista sa che puo` capitare in tutti i sistemi di sincronizzazione. Ne puo` calcolare la probabilita` e se e` troppo alta puo` ridurre la propbabilita` di errore, ma non puo` fare nulla per garantire che tsu del primo FF sia soddisfatto.

[quote="Gost91"]

Per il secondo registro le condizioni da rispettare sono:

[list=1][*]tempo per campionare correttamente l'ingresso:

;

;Solo questa la seconda non c'entra. Se vuoi aggiungere una seconda condizione e` la stessa di prima, sulla frequenza e la durata dei livelli del segnale di clock. In alcuni casi addirittura il periodo minimo di clock puo` essere leggermente minore del tempo di propagazione.

[quote="Gost91"]

Per far funzionare l'n-esimo registro di uno shift register allora dovrebbero valere le condizioni:

[list=1][*]tempo per campionare correttamente l'ingresso: [unparseable or potentially dangerous latex formula];

Solo questa! Se viene rispettato la durata minima degli impulsi, il FF commuta correttamente.

Il Tclk minimo in un FF puo` essere minore del tempo di propagazione tCQ. Questo vuol dire che il FF funziona correttamente anche se il segnale dovesse uscire dopo il fronte successivo a causa dei ritardi. Basta saperlo!. Se il FF e` non e` "da solo" ma in un sistema sincrono, allora bisogna che Tclk sia aumentato per dare il tempo al segnale di uscire e arrivare con congruo anticipo al FF successivo. Ma un FF da solo puo` lavorare con il segnale di uscita che cambia DOPO il fronte successivo.

[quote="Gost91"]

Magari si può fare un discorso pratico, dicendo che più o meno i tempi di setup e di propagazione sono simili...

No, nessun discorso pratico o approssimazioni varie. Bisogna solo rispettare due condizioni, sempre: la durata degli impulsi maggiore della durata minima, e i dati in ingresso al FF devono arrivare con sufficiente anticipo rispetto al fronte attivo e rimanere stabili abbastanza dopo il fronte. Questo secondo intervallo spesso e` nullo o negativo.

Nel caso di un registro a scorrimento, sincrono, vuol dire verificare che

[unparseable or potentially dangerous latex formula] a partire dal secondo FF in avanti.

Purtroppo per me i dubbi non finiscono, avrei bisogno di una mano anche con il prossimo esempio.

Un quarto esempio

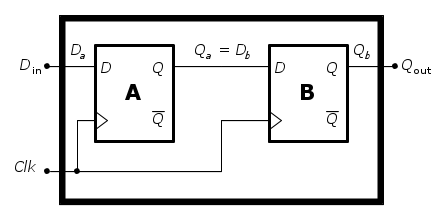

Credo che per completare la casistica resti da analizzare una rete asincrona, come quella del divisore di frequenza per 4, il cui schema è il seguente.

Una temporizzazione per il primo registro è la seguente

Come visto nel secondo esempio, il primo registro funziona se .

.

La relativa temporizzazione del secondo registro è la seguente.

Le condizioni per cui il secondo registro funziona correttamente mi paiono più complicate da ricavare in quanto non è certo dove cade il colpo clock attivo. Ora iniziano i dubbi, in quanto non so trattare il tempo di setup del secondo registro. Mi viene da fare il seguente ragionamento: nel caso peggiore, il clock commuta senza il ritardo di propagazione , quindi l'ingresso Db viene sentito se commuta nella finestra di tempo che va da un colpo di clock triggerante e [unparseable or potentially dangerous latex formula].

, quindi l'ingresso Db viene sentito se commuta nella finestra di tempo che va da un colpo di clock triggerante e [unparseable or potentially dangerous latex formula].

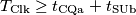

Il secondo registro funziona se:

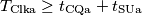

Nel complesso allora il sistema funziona se sono soddisfatte simultaneamente le relazioni

I clock dei due registri sono legati al segnale di clock del sistema per mezzo delle relazioni

, pertanto il sistema precedente si riscrive come

, pertanto il sistema precedente si riscrive come

[unparseable or potentially dangerous latex formula]

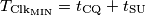

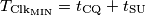

quindi il minimo periodo di clock per il quale il sistema funziona correttamente è

[unparseable or potentially dangerous latex formula]

nel caso di FF identici, l'espressione si riduce alla seguente

dalla quale si capisce che il punto critico del sistema è il primo registro, nel senso che se il primo registro funziona allora anche il secondo registro funziona.

Un quarto esempio

Credo che per completare la casistica resti da analizzare una rete asincrona, come quella del divisore di frequenza per 4, il cui schema è il seguente.

Una temporizzazione per il primo registro è la seguente

Come visto nel secondo esempio, il primo registro funziona se

.

.La relativa temporizzazione del secondo registro è la seguente.

Le condizioni per cui il secondo registro funziona correttamente mi paiono più complicate da ricavare in quanto non è certo dove cade il colpo clock attivo. Ora iniziano i dubbi, in quanto non so trattare il tempo di setup del secondo registro. Mi viene da fare il seguente ragionamento: nel caso peggiore, il clock commuta senza il ritardo di propagazione

, quindi l'ingresso Db viene sentito se commuta nella finestra di tempo che va da un colpo di clock triggerante e [unparseable or potentially dangerous latex formula].

, quindi l'ingresso Db viene sentito se commuta nella finestra di tempo che va da un colpo di clock triggerante e [unparseable or potentially dangerous latex formula].Il secondo registro funziona se:

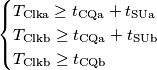

- c'è il tempo di campionare l'ingresso:

;

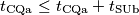

; - c'è il tempo per far commutare l'uscita:

.

.

Nel complesso allora il sistema funziona se sono soddisfatte simultaneamente le relazioni

I clock dei due registri sono legati al segnale di clock del sistema per mezzo delle relazioni

, pertanto il sistema precedente si riscrive come

, pertanto il sistema precedente si riscrive come[unparseable or potentially dangerous latex formula]

quindi il minimo periodo di clock per il quale il sistema funziona correttamente è

[unparseable or potentially dangerous latex formula]

nel caso di FF identici, l'espressione si riduce alla seguente

dalla quale si capisce che il punto critico del sistema è il primo registro, nel senso che se il primo registro funziona allora anche il secondo registro funziona.

rispondigli anche a questo, è importantissimo ! Così riesce ad avere i riferimenti per risponderti al meglio;

vedi l'ultima parte della sua firma

La formula 2 non va bene perche' il tempo di set up del FF A non lo puoi garantire con sicurezza. Il segnale Da arriva dall'esterno, e` asincrono, non puoi dire nulla. Vale a dire che il primo flip flop funziona come puo`, non e` sotto il tuo controllo.

Sono d'accordo. Basta dire che in un eventuale progetto bisogna fare in modo che l'ingresso D=Da dello shift register commuti con sufficiente anticipo rispetto il prossimo fronte di clock.

Per la precisione, l'ingresso deve commutare nella finestra di tempo che va da un fronte di clock e

. Però questo pone già una condizione sul periodo di clock: deve essere almeno

. Però questo pone già una condizione sul periodo di clock: deve essere almeno  .

.La formula 2 non va bene perche' il tempo di set up del FF A non lo puoi garantire con sicurezza. L'uscita del primo FF, Qa, non torna su Da e quindi il tempo di set up di A non c'entra nelle formule e una espressione tCQa+tsua non ha senso dato che Qa non torna su Da.

tCQa e` il ritardo con cui il primo FF (A) da` il segnale al secondo FF (B), e questo deve essere stabile prima che inizi tsuB.

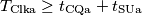

Nel caso a due FF, il solo FF di cui puoi garantire il corretto funzionamento e` il secondo, che funziona bene se Qa arriva prima dell'inizio del set up di B, quindi Tck>tCQa+tSUb.

Ok, spero di aver capito dove sta l'errore. Ho sbagliato a combinare tra loro le condizioni da rispettare (e conseguentemente anche il primo esempio in [1] è sbagliato).

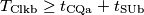

Per il primo registro le condizioni da rispettare sono:

- tempo per campionare correttamente l'ingresso:

;

; - tempo per far commutare correttamente l'uscita:

.

.

Per il secondo registro le condizioni da rispettare sono:

- tempo per campionare correttamente l'ingresso:

;

; - tempo per far commutare correttamente l'uscita:

.

.

Il periodo minimo di clock dovrebbe quindi essere

[unparseable or potentially dangerous latex formula]

avendo sfruttato il fatto che, per la positività dei tempi, si ha

.

.Nel caso a due FF, il solo FF di cui puoi garantire il corretto funzionamento e` il secondo, che funziona bene se Qa arriva prima dell'inizio del set up di B, quindi Tck>tCQa+tSUb.

Per gli altri FF il discorso e` assolutamente lo stesso. Considera questo: un FF "fa la foto" di che cosa ha su D quando arriva il fronte attivo del clock, e con un certo ritardo mette sull'uscita il dato che ha campionato. Il FF non sa da dove arriva il dato, se arriva da un altro FF o da un'altra parte. Se vengono rispettati tSU e tH al SUO ingresso, lui butta fuori dopo tCQ il dato, indipendentemente da tutto il resto.

Il FF e` miope, non vede da dove arrivano i segnali. Quando c'e` il fronte del clock, fa la foto dell'ingresso e se i tempi di set up e hold sono rispettati la foto viene bene, non mossa.

Questo vuol dire che se metti tanti FF in cascata ciascuno vede SOLO il suo ingresso, e butta fuori il risultato con il SUO ritardo. Se tutti i FF sono uguali, tutti hanno lo stesso ritardo, i dati escono tutti contemporaneamente.

Per far funzionare l'n-esimo registro di uno shift register allora dovrebbero valere le condizioni:

- tempo per campionare correttamente l'ingresso: [unparseable or potentially dangerous latex formula];

- tempo per far commutare correttamente l'uscita:

.

.

Il periodo minimo di clock per uno shift register ''a 4 bit'' allora è

[unparseable or potentially dangerous latex formula]

i termini da confrontare sono tutti tempi nonnegativi, per cui l'espressione si semplifica nella seguente

[unparseable or potentially dangerous latex formula]

Questa assomiglia di più al risultato su gli appunti, però ancora non coincide. Magari si può fare un discorso pratico, dicendo che più o meno i tempi di setup e di propagazione sono simili, per cui alla fine

[unparseable or potentially dangerous latex formula]

Dalle figure che hai fatto sembra che consideri che i tCQ dipendano da quanto ritardo c'e` dovuto ad altri FF precendenti. Questo non capita, ogni FF risincronizza i dati, e tCQ e` sempre lo stesso, indipendentemente da dove e`messo il FF nella catena.

Sì, questa l'avevo presa. Ti ringrazio nuovamente per il prezioso, e sempre più fondamentale, aiuto che mi stai dando.

Gli appunti sono giusti.

La formula 2 non va bene perche' il tempo di set up del FF A non lo puoi garantire con sicurezza. Il segnale Da arriva dall'esterno, e` asincrono, non puoi dire nulla. Vale a dire che il primo flip flop funziona come puo`, non e` sotto il tuo controllo. L'uscita del primo FF, Qa, non torna su Da e quindi il tempo di set up di A non c'entra nelle formule e una espressione tCQa+tsua non ha senso dato che Qa non torna su Da.

tCQa e` il ritardo con cui il primo FF (A) da` il segnale al secondo FF (B), e questo deve essere stabile prima che inizi tsuB.

Nel caso a due FF, il solo FF di cui puoi garantire il corretto funzionamento e` il secondo, che funziona bene se Qa arriva prima dell'inizio del set up di B, quindi Tck>tCQa+tSUb.

Per gli altri FF il discorso e` assolutamente lo stesso. Considera questo: un FF "fa la foto" di che cosa ha su D quando arriva il fronte attivo del clock, e con un certo ritardo mette sull'uscita il dato che ha campionato. Il FF non sa da dove arriva il dato, se arriva da un altro FF o da un'altra parte. Se vengono rispettati tSU e tH al SUO ingresso, lui butta fuori dopo tCQ il dato, indipendentemente da tutto il resto.

Il FF e` miope, non vede da dove arrivano i segnali. Quando c'e` il fronte del clock, fa la foto dell'ingresso e se i tempi di set up e hold sono rispettati la foto viene bene, non mossa.

Questo vuol dire che se metti tanti FF in cascata ciascuno vede SOLO il suo ingresso, e butta fuori il risultato con il SUO ritardo. Se tutti i FF sono uguali, tutti hanno lo stesso ritardo, i dati escono tutti contemporaneamente.

Dalle figure che hai fatto sembra che consideri che i tCQ dipendano da quanto ritardo c'e` dovuto ad altri FF precendenti. Questo non capita, ogni FF risincronizza i dati, e tCQ e` sempre lo stesso, indipendentemente da dove e` messo il FF nella catena.

In quale ateneo sei e quale corso segui?

La formula 2 non va bene perche' il tempo di set up del FF A non lo puoi garantire con sicurezza. Il segnale Da arriva dall'esterno, e` asincrono, non puoi dire nulla. Vale a dire che il primo flip flop funziona come puo`, non e` sotto il tuo controllo. L'uscita del primo FF, Qa, non torna su Da e quindi il tempo di set up di A non c'entra nelle formule e una espressione tCQa+tsua non ha senso dato che Qa non torna su Da.

tCQa e` il ritardo con cui il primo FF (A) da` il segnale al secondo FF (B), e questo deve essere stabile prima che inizi tsuB.

Nel caso a due FF, il solo FF di cui puoi garantire il corretto funzionamento e` il secondo, che funziona bene se Qa arriva prima dell'inizio del set up di B, quindi Tck>tCQa+tSUb.

Per gli altri FF il discorso e` assolutamente lo stesso. Considera questo: un FF "fa la foto" di che cosa ha su D quando arriva il fronte attivo del clock, e con un certo ritardo mette sull'uscita il dato che ha campionato. Il FF non sa da dove arriva il dato, se arriva da un altro FF o da un'altra parte. Se vengono rispettati tSU e tH al SUO ingresso, lui butta fuori dopo tCQ il dato, indipendentemente da tutto il resto.

Il FF e` miope, non vede da dove arrivano i segnali. Quando c'e` il fronte del clock, fa la foto dell'ingresso e se i tempi di set up e hold sono rispettati la foto viene bene, non mossa.

Questo vuol dire che se metti tanti FF in cascata ciascuno vede SOLO il suo ingresso, e butta fuori il risultato con il SUO ritardo. Se tutti i FF sono uguali, tutti hanno lo stesso ritardo, i dati escono tutti contemporaneamente.

Dalle figure che hai fatto sembra che consideri che i tCQ dipendano da quanto ritardo c'e` dovuto ad altri FF precendenti. Questo non capita, ogni FF risincronizza i dati, e tCQ e` sempre lo stesso, indipendentemente da dove e` messo il FF nella catena.

In quale ateneo sei e quale corso segui?

Grazie Isidoro, adesso è tutto chiaro

Ora che la questione sul tempo di hold è sistemata, avrei qualche altra domanda riguardo la massima frequenza di lavoro di alcune reti sequenziali.

Un terzo esempio

Per quanto riguarda lo shift register non mi ritrovo con gli appunti presi a lezione.

Secondo quanto scritto nei miei appunti, il minimo periodo di clock di uno shift register ''a 4 bit'' (si dice così?) sarebbe (trascurando il tempo di hold) dato dalla espressione

[unparseable or potentially dangerous latex formula]

La formula mi pare sbagliata. Lo schema di un shift register a FFD ''a 2 bit'' è il seguente.

Una temporizzazione per il primo registro è la seguente

da questa si capisce che il primo registro funziona correttamente se vale la relazione

[unparseable or potentially dangerous latex formula]

Per il secondo il registro si ha, conseguentemente alla precedente temporizzazione, la seguente temporizzazione

in questo caso il secondo registro funziona correttamente se

[unparseable or potentially dangerous latex formula]

Il sistema nel suo complesso funziona correttamente se funzionano correttamente tutte le sue parti, quindi il periodo di clock deve soddisfare simultaneamente sia la che la

che la  . Il sistema che porta al minimo periodo di clock accettato dal sistema è quindi

. Il sistema che porta al minimo periodo di clock accettato dal sistema è quindi

[unparseable or potentially dangerous latex formula]

che porta alla soluzione

[unparseable or potentially dangerous latex formula]

In base a questo risultato credo sia possibile determinare per induzione il periodo di clock minimo per il generico shift register ''a n bit''.

Considerando uno shift register ''a 3 bit'', i primi due registri danno luogo sempre alle condizioni e

e  , mentre il terzo registro da luogo alla terza condizione

, mentre il terzo registro da luogo alla terza condizione

[unparseable or potentially dangerous latex formula]

in quanto per il terzo registro si vanno a confrontare i tempi di propagazione tra l'uscita del secondo registro e quello dell'uscita del terzo registro. Se il ragionamento è corretto allora il sistema che caratterizza il minimo periodo di clock accettato dallo shift register ''a n bit'' è

[unparseable or potentially dangerous latex formula]

che porta alla seguente soluzione

[unparseable or potentially dangerous latex formula]

questa espressione per lo shift register ''a 4 bit'' si riduce alla seguente

[unparseable or potentially dangerous latex formula]

che non è in accordo con il risultato riportato su i miei appunti.

Ora che la questione sul tempo di hold è sistemata, avrei qualche altra domanda riguardo la massima frequenza di lavoro di alcune reti sequenziali.

Un terzo esempio

Per quanto riguarda lo shift register non mi ritrovo con gli appunti presi a lezione.

Secondo quanto scritto nei miei appunti, il minimo periodo di clock di uno shift register ''a 4 bit'' (si dice così?) sarebbe (trascurando il tempo di hold) dato dalla espressione

[unparseable or potentially dangerous latex formula]

La formula mi pare sbagliata. Lo schema di un shift register a FFD ''a 2 bit'' è il seguente.

Una temporizzazione per il primo registro è la seguente

da questa si capisce che il primo registro funziona correttamente se vale la relazione

[unparseable or potentially dangerous latex formula]

Per il secondo il registro si ha, conseguentemente alla precedente temporizzazione, la seguente temporizzazione

in questo caso il secondo registro funziona correttamente se

[unparseable or potentially dangerous latex formula]

Il sistema nel suo complesso funziona correttamente se funzionano correttamente tutte le sue parti, quindi il periodo di clock deve soddisfare simultaneamente sia la

che la

che la  . Il sistema che porta al minimo periodo di clock accettato dal sistema è quindi

. Il sistema che porta al minimo periodo di clock accettato dal sistema è quindi[unparseable or potentially dangerous latex formula]

che porta alla soluzione

[unparseable or potentially dangerous latex formula]

In base a questo risultato credo sia possibile determinare per induzione il periodo di clock minimo per il generico shift register ''a n bit''.

Considerando uno shift register ''a 3 bit'', i primi due registri danno luogo sempre alle condizioni

e

e  , mentre il terzo registro da luogo alla terza condizione

, mentre il terzo registro da luogo alla terza condizione[unparseable or potentially dangerous latex formula]

in quanto per il terzo registro si vanno a confrontare i tempi di propagazione tra l'uscita del secondo registro e quello dell'uscita del terzo registro. Se il ragionamento è corretto allora il sistema che caratterizza il minimo periodo di clock accettato dallo shift register ''a n bit'' è

[unparseable or potentially dangerous latex formula]

che porta alla seguente soluzione

[unparseable or potentially dangerous latex formula]

questa espressione per lo shift register ''a 4 bit'' si riduce alla seguente

[unparseable or potentially dangerous latex formula]

che non è in accordo con il risultato riportato su i miei appunti.

[quote="Gost91"]

Questo non va contro la condizione data dal tempo di setup?

Questo non va contro la condizione data dal tempo di setup?

No, perche' il tempo di setup e` maggiore di quello (negativo) di hold. Supponi di avere tsu=30ns e th=-5ns. Questo vuol dire che il dato deve essere stabile nella finestra che va da 30ns prima a 5 ns prima del dato. Potrebbe essere che il segnale di clock vada direttamente sul "core" del FF, mentre il dato passa attraversa un paio di porte che lo ritardano.

Non ho capito bene a quale tempo di propagazione ti riferisci.

Tempo fra clock e dato.

Se il tempo di propagazione di cui parli fosse...

Dovevo dire tempo di propagazione minimo.

A questo punto il tempo di hold e` rispettato anche nel divisore. Quasi mai il tempo di propagazione minimo e` dichiarato, ma il costruttore talvolta in qualche noticina garantisce il funzionamento dei sistemi sincroni, in cui Q va su D e i clock sono uguali.

Ti ringrazio per la risposta, però purtroppo non mi è ancora molto chiara la faccenda.

Grazie, ma mi sono venuti un po' ''minuscoli''

Questo non va contro la condizione data dal tempo di setup?

Non ho capito bene a quale tempo di propagazione ti riferisci. Se il tempo di propagazione di cui parli fosse allora mi verrebbe da dire che, indipendentemente dal fatto che questo sia maggiore, minore o uguale al tempo di hold, il sistema non potrebbe ancora funzionare.

allora mi verrebbe da dire che, indipendentemente dal fatto che questo sia maggiore, minore o uguale al tempo di hold, il sistema non potrebbe ancora funzionare.

Sia nel caso che nel caso

che nel caso  l'ingresso può variare all'interno dell'intervallo proibito

l'ingresso può variare all'interno dell'intervallo proibito  . Se

. Se  , l''unica è che

, l''unica è che  sia nullo (cosa impossibile nella pratica).

sia nullo (cosa impossibile nella pratica).

Complimenti per i disegni!

Grazie, ma mi sono venuti un po' ''minuscoli''

le cose funzionano perche' se vai a vedere il th di un FFD spesso e` negativo, che vuol dire che il dato puo` cambiare addirittura subito prima del clock.

Questo non va contro la condizione data dal tempo di setup?

Se si devono fare dei progetti "veri" garantiti che funzionino, nel caso del divisore bisogna verificare che il tempo di propagazione minimo sia comunque maggiore del tempo di hold.

Non ho capito bene a quale tempo di propagazione ti riferisci. Se il tempo di propagazione di cui parli fosse

allora mi verrebbe da dire che, indipendentemente dal fatto che questo sia maggiore, minore o uguale al tempo di hold, il sistema non potrebbe ancora funzionare.

allora mi verrebbe da dire che, indipendentemente dal fatto che questo sia maggiore, minore o uguale al tempo di hold, il sistema non potrebbe ancora funzionare. Sia nel caso

che nel caso

che nel caso  l'ingresso può variare all'interno dell'intervallo proibito

l'ingresso può variare all'interno dell'intervallo proibito  . Se

. Se  , l''unica è che

, l''unica è che  sia nullo (cosa impossibile nella pratica).

sia nullo (cosa impossibile nella pratica).