FSK VHDL

Ciao a tutti.

Ho realizzato in VHDL un trasmettitore FSK ad onda quadra, e ora ho un problema.

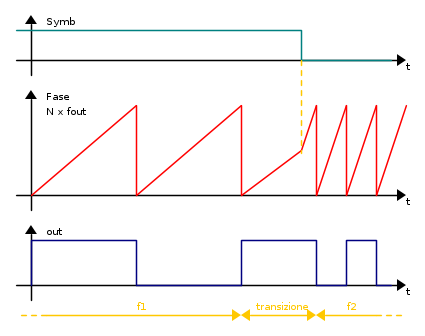

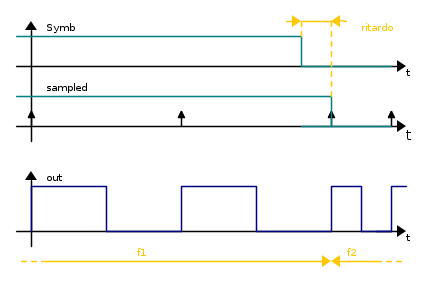

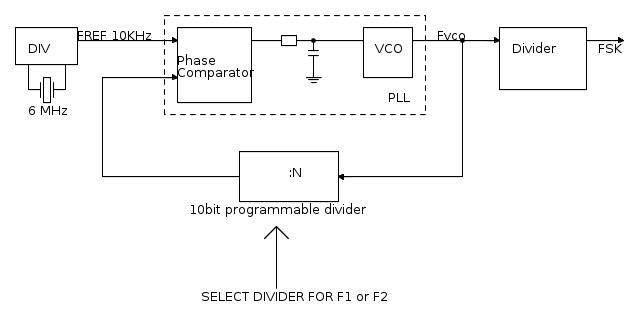

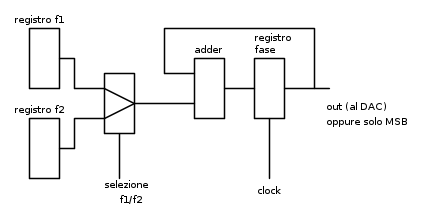

Come si può garantire la continuità di fase quando il messaggio trasmesso passa da una frequenza ad un'altra?

Le due frequenze sono ad esempio 5Khz per lo 0 logico e 16 kHz per l'1 logico.

Esiste un metodo per rendere questa transizione morbida?

Grazie mille fatemi sapere

Ho realizzato in VHDL un trasmettitore FSK ad onda quadra, e ora ho un problema.

Come si può garantire la continuità di fase quando il messaggio trasmesso passa da una frequenza ad un'altra?

Le due frequenze sono ad esempio 5Khz per lo 0 logico e 16 kHz per l'1 logico.

Esiste un metodo per rendere questa transizione morbida?

Grazie mille fatemi sapere