Tempo di commutazione HL (cmos)

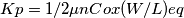

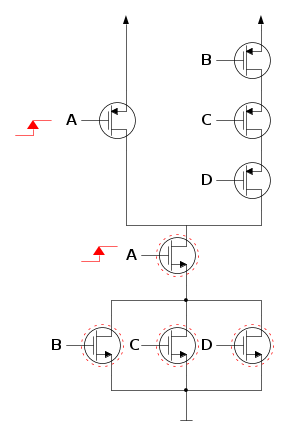

Salve a tutti, ho un dubbio riguardo la seguente porta logica in tecnologia Cmos che realizza la funzione Y=A(B+C+D) negata.

Voglio calcolare il tempo di commutazione nel caso in cui B=C=D=1 e A va da 0 a 1 .

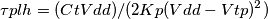

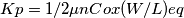

Dunque per A=0 --> Y=0 e per A=1 --> Y=1 , dovro' quindi ricavare il tempo di commutazione HL come segue :

nel calcolo di

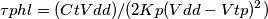

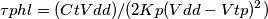

devo calcolare :

e qui sorge il mio dubbio, dovendo guardare la rete Pmos , i pmos in conduzione saranno tutt e 4 ?

e quindi il mio = 1/RonA//(RonB+RonC+RonD) ? ? ?

= 1/RonA//(RonB+RonC+RonD) ? ? ?

grazie mille per l'attenzione .

PS: Mi scuso con i moderatori ma non sono riuscito a graficare a dovere il circuito con fcd e sono stato costretto ad allegarlo.

Voglio calcolare il tempo di commutazione nel caso in cui B=C=D=1 e A va da 0 a 1 .

Dunque per A=0 --> Y=0 e per A=1 --> Y=1 , dovro' quindi ricavare il tempo di commutazione HL come segue :

nel calcolo di

devo calcolare :

e qui sorge il mio dubbio, dovendo guardare la rete Pmos , i pmos in conduzione saranno tutt e 4 ?

e quindi il mio

= 1/RonA//(RonB+RonC+RonD) ? ? ?

= 1/RonA//(RonB+RonC+RonD) ? ? ?grazie mille per l'attenzione .

PS: Mi scuso con i moderatori ma non sono riuscito a graficare a dovere il circuito con fcd e sono stato costretto ad allegarlo.

devi considerare

devi considerare  e non

e non  .

.