Rispondo per quel che riguarda i circuiti digitali.

Un moderno circuito CMOS ha due tipi di consumo di corrente: statico e dinamico.

Il consumo statico è dato da fenomeni come il leakage e non ci interessa quando parliamo di condensatori di disaccoppiamento.

Il consumo dinamico è dato da due componenti: carico capacitivo e shoot-through.

Il carico sono le capacità dovute ai gate che vengono pilotati dall'uscita del circuito che stiamo considerando.

Il shoot-through è quel fenomeno per cui per un brevissimo intervallo di tempo sia i transistor di tipo N che quelli di tipo P conducono. Si ha allora un collegamento tra Vdd e Vss e quindi un picco di corrente.

I chip sono saldati alle piste di un PCB. L'impedenza di queste piste non è nulla ed ad essa si somma l'impedenza del chip stesso (bonding, padframe).

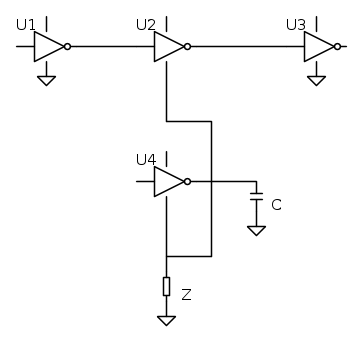

Prendiamo un esempio concreto:

C è il carico pilotato da U4.

Z è l'impedenza parassita. Se supponiamo che U2 e U4 sono vicini (o addirittura nello stesso package!), la possiamo considerare comune ai due.

SItuazione iniziale: U4 ha uno 0 in entrata.

L'entrata di U4 commuta a 1, così che l'uscita viene portata a 0.

C si scarica rapidamente attraverso U4 e attraverso Z.

Su Z appare una caduta di tensione, che viene vista anche da U2.

Il threshold di ingresso di U2 si sposta di conseguenza e, se siamo sfortunati raggiunge il livello logico generato da U1. A questo punto abbiamo un glitch in uscita a U2, che tramite U3 si propaga alla logica a valle.

Oggi non è venerdì 13 e quindi non siamo sfortunati. C'è però un altro fenomeno che può portare U3 a vedere il falso valore in entrata. La caduta di tensione su Z alza il potenziale di riferimento di U4 e di conseguenza anche il suo Vol. Se la caduta di tensione è maggiore o uguale al noise margin dei gate, la probabilità di avere glitch è alta.

Come vedi, l'impedenza sulle linee di alimentazione la vogliamo evitare come la peste.

Per inciso il fenomeno si verifica esattamente allo stesso modo sulla linea di alimentazione positiva. Il termine generico per descrivere il problema è "ground bounce".

Per evitarlo ci sono diverse tecniche. La piú comune è proprio il condensatore di disaccoppiamento. E il motivo per cui va messo vicino al chip è proprio la riduzione dell'impedenza parassita.

Un'analisi non è facile perché vanno considerati vari valori di difficile stima. Piú tardi vedo se trovo qualcosa...

DImensionamento: attieniti al datasheet del componente

Facezie a parte (che poi non sono facezie, è il modo migliore di ottenere il risultato voluto!), i condensatori non sono capacità. Sono un compicato insieme di capacità, ESR e ESL. Hanno quindi una frequenza di risonanza, oltre alla quale si comportano piú come induttori che come capacità!

La formula magica sta nel combinare condensatori di vario tipo e capacità, in modo da coprire tutto lo spettro di interesse. Si parte con i grossi elettrolitici dell'alimentazione, si passa alla manciata di microfarad sulla scheda, scendeno poi ai classici 100 nF nei pressi del chip per arrivare alle capacità integrate nel package e ai fill-cap sul die.

A questo proposito segnalo i condensatori X2Y, fatti apposta per questo e aventi una ESL particolarmente bassa. Da qualche parte sul sito della Johanson Dielectrics c'è un'application note.

Un altro stratagemma è aumentare ad hoc la ESR per diminuire il fattore di merito. È una lama a doppio taglio, anche la ESR genera ground bounce!

Per finire, un ottimo tool per fare un po' di simulazioni è questo:

http://www.altera.com/technology/signal ... l-pdn.htmlSaluti Boiler