Clock Skew

Salve ragazzi, innanzitutto complimenti a tutti per il forum, mi è stato di aiuto molte volte in passato.

Volevo domandarvi qualche delucidazione sul concetto di clock skew, in particolare quali solo le relazioni matematiche che devono essere rispettate per il corretto funzionamento del circuito. Lo domando perché il mio docente nell'ultimo appello ha inserito una richiesta, "verificare se il circuito funziona oppure se ci sono problemi causati da clock skew". Ora, poiché durante il corso, tenuto da un altro docente, di clock skew non se ne è sentito mai neanche l'eco, tutti abbiamo saltato quella richiesta non sapendo quanto valesse effettivamente a livello di punteggio. Cercando in internet ho più o meno capito che si tratta di un problema dovuto al ritardo di propagazione del clock quando è condiviso tra diversi flip flops. In poche parole il clock non arriva contemporaneamente ad entrambi i flip flop e questo causa problemi alla corretta acquisizione dei dati.

Potreste per favore aiutarmi a tradurre questa cosa in relazioni matematiche, tenendo conto di entrambe le possibili direzioni della propagazione dei dati? Grazie mille, so che probabilmente la domanda è scema, ma non riesco proprio a capire.

Volevo domandarvi qualche delucidazione sul concetto di clock skew, in particolare quali solo le relazioni matematiche che devono essere rispettate per il corretto funzionamento del circuito. Lo domando perché il mio docente nell'ultimo appello ha inserito una richiesta, "verificare se il circuito funziona oppure se ci sono problemi causati da clock skew". Ora, poiché durante il corso, tenuto da un altro docente, di clock skew non se ne è sentito mai neanche l'eco, tutti abbiamo saltato quella richiesta non sapendo quanto valesse effettivamente a livello di punteggio. Cercando in internet ho più o meno capito che si tratta di un problema dovuto al ritardo di propagazione del clock quando è condiviso tra diversi flip flops. In poche parole il clock non arriva contemporaneamente ad entrambi i flip flop e questo causa problemi alla corretta acquisizione dei dati.

Potreste per favore aiutarmi a tradurre questa cosa in relazioni matematiche, tenendo conto di entrambe le possibili direzioni della propagazione dei dati? Grazie mille, so che probabilmente la domanda è scema, ma non riesco proprio a capire.

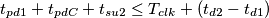

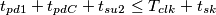

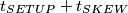

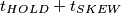

e il tempo di hold

e il tempo di hold

il ritardo dalla sorgente del clock al FF *

il ritardo dalla sorgente del clock al FF * il propagation delay

il propagation delay il periodo del clock

il periodo del clock il setup time

il setup time lo skew

lo skew