Flip-flop JK: problemi di temporizzazione

Salve a tutti ,

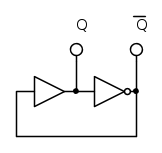

avrei a breve un esame di elettronica digitale , sono alle prese con lo studio dei flip flop e non riesco a capire dal libro in cosa consistono questi problemi di temporizzazione, riporto in allegato immagine del libro (P.Spirito) in cui sono fatti due esempi, uno relativo ad entrambi gli ingressi alti e viceversa.

Sarei veramente grato se qualcuno riuscisse a spiegarmi il motivo per cui l impulso di clock deve avere una durata compresa tra i 2Tp e i 3Tp (TAU ) per evitare inversioni successive.

Se posso fornire altre informazioni in merito alla spiegazione del libro sono piu' che disponibile pur di riuscire a comprendere questa problematica.

grazie mille

avrei a breve un esame di elettronica digitale , sono alle prese con lo studio dei flip flop e non riesco a capire dal libro in cosa consistono questi problemi di temporizzazione, riporto in allegato immagine del libro (P.Spirito) in cui sono fatti due esempi, uno relativo ad entrambi gli ingressi alti e viceversa.

Sarei veramente grato se qualcuno riuscisse a spiegarmi il motivo per cui l impulso di clock deve avere una durata compresa tra i 2Tp e i 3Tp (TAU ) per evitare inversioni successive.

Se posso fornire altre informazioni in merito alla spiegazione del libro sono piu' che disponibile pur di riuscire a comprendere questa problematica.

grazie mille