Circuito start-stop contatore

Ciao a tutti, per il solito progetto universitario sto progettando un contatore che mi permetta di determinare con precisione lo sfasamento tra due segnali, nello specifico devo contare il numero di colpi di clock che intercorrono tra due fronti di salita di 2 segnali.

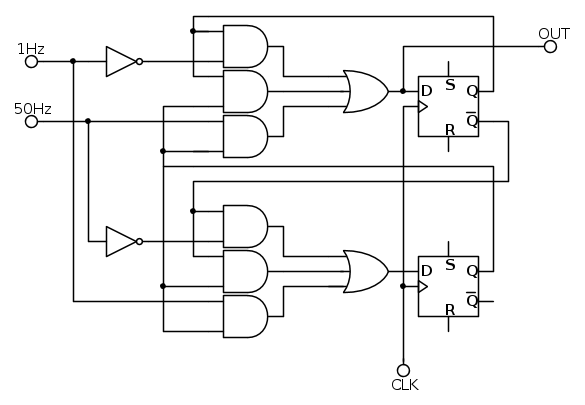

Il primo segnale è a 1Hz, il secondo segnale è a 50Hz, il clock è a 20MHz. prendendo un contatore ad esempio un 4040 è facile contare solo ed esclusivamente il periodo che intercorre tra i due fronti, basta tramite una porta AND passarci dentro il clock e un segnale di abilitazione che vada alto al fronte di salita del primo segnale e scenda al fronte di salita del secondo.

Sono giusto alla conclusione del mio ragionamento con questo circuito:

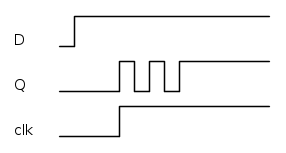

Però l'affidabilità dipende inversamente dalla larghezza dell'impulso che dovrei cercare di tenere attorno all'ordine dei nanosecondi.

Avete qualche idea su come fare?

Modifico il messaggio per aggiungere una breve spiegazione del circuito.

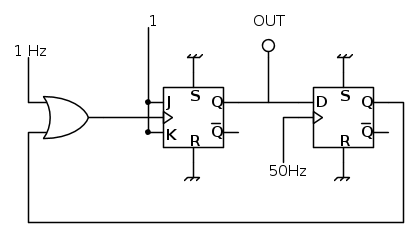

Ipotizzo che OUT sia a livello LOW, ad ogni colpo di 50Hz il flipflop D continuerà ad aggiornare il suo Q con il valore 0 (ingresso DATA). All'ingresso della OR avrò quindi uno 0, ogni cambiamento del clock ad 1Hz si ripercuoterà direttamente sul JK. Il clock 50Hz è praticamente disabilitato, non ha effetto sull'uscita.

Nel momento in cui arriva un fronte di salita del clock 1Hz il flipflop JK (in configurazione TOGGLE) commuta le uscite invertendole (in questo caso da 0 a 1).

Al successivo colpo di clock 50Hz (e so che sicuramente viene prima questo clock per ovvie ragioni matematiche) il flipflop D commuta l'uscita da 0 a 1. Questo passaggio da 0 a 1 non è altro che un fronte di salita per il JK che commuterà di nuovo, in questo caso da 1 a 0, finendo nello stato stabile.

Il problema si presenta se l'impulso da 1Hz è troppo lungo che si sovrappone al clock di salita dell'impulso a 50Hz successivo, in tal caso il passaggio da 0 a 1 della commutazione del flipflop D sarebbe mascherato dal livello alto che ha ancora il segnale a 1Hz.

Il primo segnale è a 1Hz, il secondo segnale è a 50Hz, il clock è a 20MHz. prendendo un contatore ad esempio un 4040 è facile contare solo ed esclusivamente il periodo che intercorre tra i due fronti, basta tramite una porta AND passarci dentro il clock e un segnale di abilitazione che vada alto al fronte di salita del primo segnale e scenda al fronte di salita del secondo.

Sono giusto alla conclusione del mio ragionamento con questo circuito:

Però l'affidabilità dipende inversamente dalla larghezza dell'impulso che dovrei cercare di tenere attorno all'ordine dei nanosecondi.

Avete qualche idea su come fare?

Modifico il messaggio per aggiungere una breve spiegazione del circuito.

Ipotizzo che OUT sia a livello LOW, ad ogni colpo di 50Hz il flipflop D continuerà ad aggiornare il suo Q con il valore 0 (ingresso DATA). All'ingresso della OR avrò quindi uno 0, ogni cambiamento del clock ad 1Hz si ripercuoterà direttamente sul JK. Il clock 50Hz è praticamente disabilitato, non ha effetto sull'uscita.

Nel momento in cui arriva un fronte di salita del clock 1Hz il flipflop JK (in configurazione TOGGLE) commuta le uscite invertendole (in questo caso da 0 a 1).

Al successivo colpo di clock 50Hz (e so che sicuramente viene prima questo clock per ovvie ragioni matematiche) il flipflop D commuta l'uscita da 0 a 1. Questo passaggio da 0 a 1 non è altro che un fronte di salita per il JK che commuterà di nuovo, in questo caso da 1 a 0, finendo nello stato stabile.

Il problema si presenta se l'impulso da 1Hz è troppo lungo che si sovrappone al clock di salita dell'impulso a 50Hz successivo, in tal caso il passaggio da 0 a 1 della commutazione del flipflop D sarebbe mascherato dal livello alto che ha ancora il segnale a 1Hz.

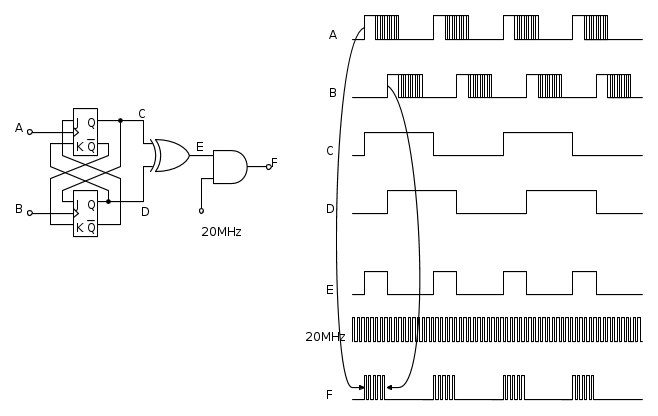

e

e  hai un fianco positivo, viceversa uno negativo). Questo è uno degli input (sincronizzati a 20 MHz) della tua FSM (che viaggia a 20 MHz). L'altro input è la stessa cosa fatta sull'altro ingresso.

hai un fianco positivo, viceversa uno negativo). Questo è uno degli input (sincronizzati a 20 MHz) della tua FSM (che viaggia a 20 MHz). L'altro input è la stessa cosa fatta sull'altro ingresso.