[Elettronica Digitale] Tempi indicati in tabella.

Salve, devo svolgere un esercizio di elettroncia digitale. Il testo dice che devo calcolare la massima frequenza di clok del circuito in allegato.

Ora prima di iniziare a risolvere l'esercizio, visto che ho solo appunti vari, sono andato a vedere cosa significassero tutti quei tempi riportati in tabella, ma sto facendo confusione. In pratica vorrei accertarmi di 3 cose:

0 - Se le spiegazioni dei tempi trovate in rete siano corrette.

1 - Se la formula della frequenza massima è corretta.

2 - Come calcolare il critical path.

Fan-IN: E' il minimo numero di ingressi relativi ad una porta logica.

Fan-OUT: Esprime il massimo carico che una porta è in grado di sopportare, funzionando correttamente.

Load Factor: Carico medio diviso il carico di picco per un periodo di tempo specificato.

Tempo di setup: Periodo minimo di tempo per il quale gli ingressi sincroni e quelli asincroni devono essere stabiliti per fare in modo che il flip-flop risponda in modo affidabile prima della transizione di clock.

Tempo di Hold: Tempo per il quale il dato deve essere stabile dopo il fronte di clock.

Tempo di Propagazione: tempo che passa tra la variazione dello stato di un ingresso e il mutamento dello stato di uscita. (H -> L, L -> H).

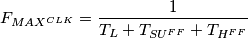

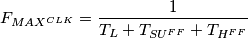

Espressione per il cacolo della massima frequenza di clock:

Dove: è il tempo della logica, ossia il critical path.

è il tempo della logica, ossia il critical path.

è il tempo di setup del flip-flop.

è il tempo di setup del flip-flop.

è il tempo di Hold del flip-flop.

è il tempo di Hold del flip-flop.

Ora vorrei sapere se le definizioni e l'espressione sono corrette per almeno avere una base da dove partire.

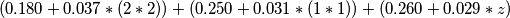

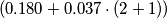

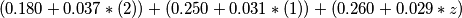

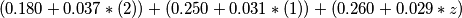

Per il calcolo del critical path se ho capito bene devo prendere il percorso più lungo. Che credo sia dato dalla porta NAND (TrH L) + XOR (TrHL) + OR (TrHL) e l'ho calcolato così:

con z = 1 ottengo:

con z = 1 ottengo:

Il 2 è relativo alle porte logiche strettamente collegate alla AND ( quindi la XOR e la NOR)

L'1 è relativo alla porta strettamente collegata alla XOR (quindi solo la OR).

Ne avevo calcolati altri di crital path:

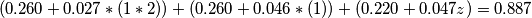

NAND (TrLH) + XOR (TrLH) + OR (TrLH) e ottengo:

NAND (TrLH) + XOR (TrHL) + OR (TrHL) e ottengo: 0.816

Ho preso il più grande.

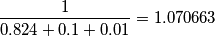

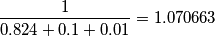

Quindi poi dalla formula della frequenza massima:

Ma devo seguire una logica per calcolarlo o basta che vado a tentativi?

Inoltre non ho usato né Fan_in né Fan-out né Load Factor né size. A cosa servono di preciso e quando?

Scusate la confusione ma sono all'inizio e sto cercando di capire il più possibile.

Grazie della disponibilità.

Ora prima di iniziare a risolvere l'esercizio, visto che ho solo appunti vari, sono andato a vedere cosa significassero tutti quei tempi riportati in tabella, ma sto facendo confusione. In pratica vorrei accertarmi di 3 cose:

0 - Se le spiegazioni dei tempi trovate in rete siano corrette.

1 - Se la formula della frequenza massima è corretta.

2 - Come calcolare il critical path.

Fan-IN: E' il minimo numero di ingressi relativi ad una porta logica.

Fan-OUT: Esprime il massimo carico che una porta è in grado di sopportare, funzionando correttamente.

Load Factor: Carico medio diviso il carico di picco per un periodo di tempo specificato.

Tempo di setup: Periodo minimo di tempo per il quale gli ingressi sincroni e quelli asincroni devono essere stabiliti per fare in modo che il flip-flop risponda in modo affidabile prima della transizione di clock.

Tempo di Hold: Tempo per il quale il dato deve essere stabile dopo il fronte di clock.

Tempo di Propagazione: tempo che passa tra la variazione dello stato di un ingresso e il mutamento dello stato di uscita. (H -> L, L -> H).

Espressione per il cacolo della massima frequenza di clock:

Dove:

è il tempo della logica, ossia il critical path.

è il tempo della logica, ossia il critical path. è il tempo di setup del flip-flop.

è il tempo di setup del flip-flop. è il tempo di Hold del flip-flop.

è il tempo di Hold del flip-flop.Ora vorrei sapere se le definizioni e l'espressione sono corrette per almeno avere una base da dove partire.

Per il calcolo del critical path se ho capito bene devo prendere il percorso più lungo. Che credo sia dato dalla porta NAND (TrH L) + XOR (TrHL) + OR (TrHL) e l'ho calcolato così:

con z = 1 ottengo:

con z = 1 ottengo:

Il 2 è relativo alle porte logiche strettamente collegate alla AND ( quindi la XOR e la NOR)

L'1 è relativo alla porta strettamente collegata alla XOR (quindi solo la OR).

Ne avevo calcolati altri di crital path:

NAND (TrLH) + XOR (TrLH) + OR (TrLH) e ottengo:

NAND (TrLH) + XOR (TrHL) + OR (TrHL) e ottengo: 0.816

Ho preso il più grande.

Quindi poi dalla formula della frequenza massima:

Ma devo seguire una logica per calcolarlo o basta che vado a tentativi?

Inoltre non ho usato né Fan_in né Fan-out né Load Factor né size. A cosa servono di preciso e quando?

Scusate la confusione ma sono all'inizio e sto cercando di capire il più possibile.

Grazie della disponibilità.