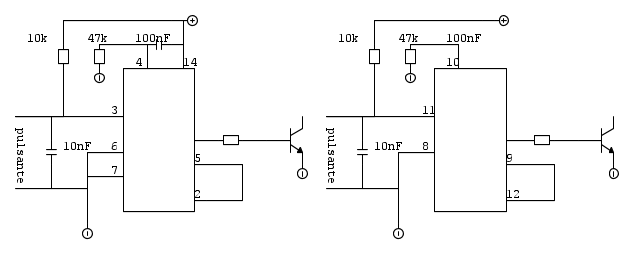

Ripeto, il circuito è una ciofeca. Il debouncing è probabilmente stato riciclato (senza capirne il funzionamento) da un circuito con un flip-flop a fianco attivo negativo. Con questi componenti siamo oltre i 100 microsecondi di raise-time. Il 4013 specifica un massimo di 10 microsecondi. Prima o poi l'insorgere di metastabilità è una garanzia.

Non parliamo poi di quella tristezza di power-on-reset.

Se permetti...

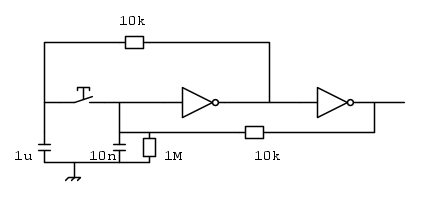

All'accensione il condensatore da 10 nF è scarico a causa del resistore da 1M in parallelo. L'ingresso del primo gate è quindi basso. Questo forza l'uscita allo stesso stato. L'unica possibilità che abbiamo di lasciare questo stato è caricare il condensatore da 10 nF, ma questo è saldamente tenuto a 0 V attraverso il resistore da 10k. Può succedere che il condensatore venga caricato durante il transiente di accensione? Se i due gates sono nello stesso package si accendono contemporaneamente e se siamo sfigati c'è un intervallo pari alla differenza dei propagation-delays durante il quale l'uscita può essere alta. Se questo intervallo eccede il tempo necessario a caricare 10 nF attraverso 10k fino al threshold del gate, allora sì, abbiamo un problema. Ma siamo due ordini di grandezza sotto. Il power-on reset è quantomento

granitico.

La commutazione avviene (ovviamente) azionando il tasto. Nel frattempo il condensatore da 1 μF si è caricato al potenziale presente al nodo tra i due gates (che è alto se l'uscita è bassa e viceversa). Premento il pulsante mettiamo in parallelo i condensatori. Uno (da 10 nF) cerca di tenere lo stato attuale, l'altro (da 1 μF) cerca di commutarlo. Credo sia chiaro chi vince

Il potenziale vincitore (ovviamente quello che era presente tra i due gates) si trova ora all'ingresso del primo gate, che commuta e porta l'uscita (attraverso il secondo gate) all'altro stato.

E ora il condensatore grosso e grasso può essere caricato al nuovo potenziale.

Ancora una parola sulla stabilità di questo circuito: l'impedenza d'ingresso si un gate CMOS è molto elevata, basta un nulla e commuta. I 10k di feedback basterebbero nel 95% dei casi a tenere lo stato ben determinato ed evitare commutazioni spurie, nel restante 5% dei casi interviene il condensatore del power-on reset a fare da blando filtro.

Questo circuito sostituisce il tuo flip-flop.

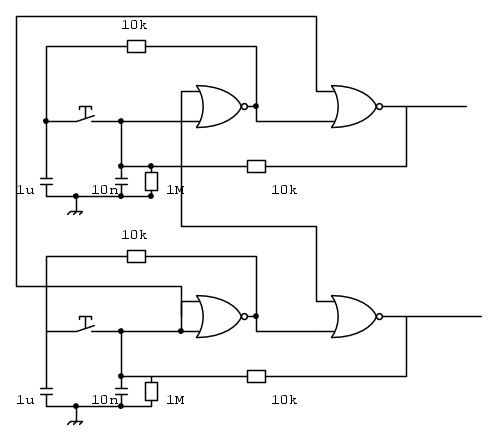

Compito a casa: usando una porte NOR si possono simulare tutti gli altri gate. Ridisegna il circuito usando porte NOR e introducendo la modifica che ti ho detto per evitare la presenza di due uscite contemporaneamente attive.

Ciao Boiler