Dimensionare CMOS

Salve a tutti  Stavo svolgendo un esercizio che mi ha mandato un po' in difficoltà,ecco perché vorrei un vostro aiuto,qualora fosse possibile

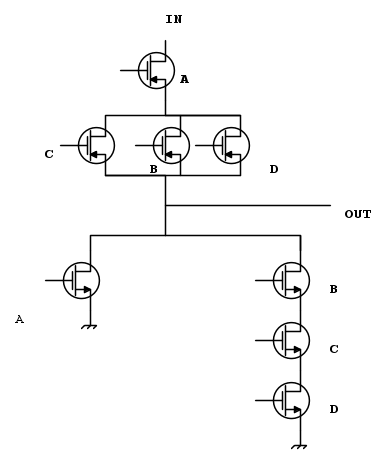

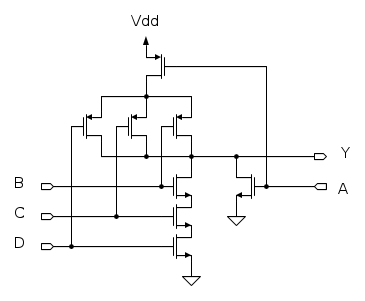

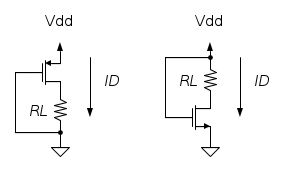

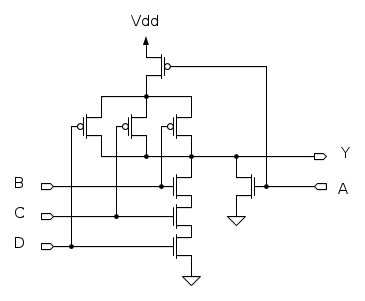

Stavo svolgendo un esercizio che mi ha mandato un po' in difficoltà,ecco perché vorrei un vostro aiuto,qualora fosse possibile  Devo realizzare la funzione logica A+BCD (la funzione è tutta negata) e dimensionare rispetto al Cmos di riferimento in modo che il ritardo medio di propagazione deve risultare pari a quello dell'invertitore di riferimento diviso 2,ossia la metà

Devo realizzare la funzione logica A+BCD (la funzione è tutta negata) e dimensionare rispetto al Cmos di riferimento in modo che il ritardo medio di propagazione deve risultare pari a quello dell'invertitore di riferimento diviso 2,ossia la metà  .

.

Il problema sorge in questo punto,non riesco a capire che ragionamento devo fare per dimensionare,avevo pensato di dividere le dimensioni di ogni transistor per 2. Ma non sono sicuro . Vi allego, il mio svolgimento..

. Vi allego, il mio svolgimento..

Devo realizzare la funzione logica A+BCD (la funzione è tutta negata) e dimensionare rispetto al Cmos di riferimento in modo che il ritardo medio di propagazione deve risultare pari a quello dell'invertitore di riferimento diviso 2,ossia la metà

Devo realizzare la funzione logica A+BCD (la funzione è tutta negata) e dimensionare rispetto al Cmos di riferimento in modo che il ritardo medio di propagazione deve risultare pari a quello dell'invertitore di riferimento diviso 2,ossia la metà Il problema sorge in questo punto,non riesco a capire che ragionamento devo fare per dimensionare,avevo pensato di dividere le dimensioni di ogni transistor per 2. Ma non sono sicuro