Esercizio punto di lavoro NMOS

Buonasera,

sto svolgendo alcuni esercizi di elettronica sui transinstor.

Ho incontrato il seguente, in cui, come primo punto, devo semplicemente calcolare il punto di lavoro del MOS. Tuttavia non ne vengo a capo.

Dunque vi espongo il mio ragionamento.

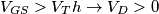

Ho notato subito che , essendo il Source collegato a massa.

, essendo il Source collegato a massa.

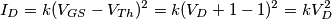

Da ciò, segue che e inoltre, essendo

e inoltre, essendo  collegata all'alimentazione, si ha

collegata all'alimentazione, si ha  .

.

Da ciò si deduce che l'NMOS è ON.

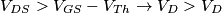

Ora, per conoscere la regione di operazione del transistor, bisogna considerare la tensione .

.

Notiamo che e quindi

e quindi

Supponiamo dapprima il transistor in saturazione. Sotto questa ipotesi, deve aversi e

e  .

.

Pertanto

Sostituendo l'espressione di nell'espressione di

nell'espressione di  ricavata, otteniamo

ricavata, otteniamo  . Pertanto il transistor non può essere in saturazione.

. Pertanto il transistor non può essere in saturazione.

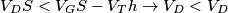

Consideriamo l'ipotesi di regione lineare. Allora

Sostituendo questo valore di nell'espressione di

nell'espressione di  , segue:

, segue:

Cioè escono valori complessi e non posso ricavare l'espressione di .

.

Quindi? dove sbaglio?

sto svolgendo alcuni esercizi di elettronica sui transinstor.

Ho incontrato il seguente, in cui, come primo punto, devo semplicemente calcolare il punto di lavoro del MOS. Tuttavia non ne vengo a capo.

Dunque vi espongo il mio ragionamento.

Ho notato subito che

, essendo il Source collegato a massa.

, essendo il Source collegato a massa.Da ciò, segue che

e inoltre, essendo

e inoltre, essendo  collegata all'alimentazione, si ha

collegata all'alimentazione, si ha  .

.Da ciò si deduce che l'NMOS è ON.

Ora, per conoscere la regione di operazione del transistor, bisogna considerare la tensione

.

.Notiamo che

e quindi

e quindi

Supponiamo dapprima il transistor in saturazione. Sotto questa ipotesi, deve aversi

e

e  .

. Pertanto

Sostituendo l'espressione di

nell'espressione di

nell'espressione di  ricavata, otteniamo

ricavata, otteniamo  . Pertanto il transistor non può essere in saturazione.

. Pertanto il transistor non può essere in saturazione.Consideriamo l'ipotesi di regione lineare. Allora

![I_D=2k[(V_{GS}-V_{Th})V_{DS}-\frac{V_{DS}^2}{2}]=2*10^{-3}[7V_{D}-\frac{V_{D}^2}{2}] I_D=2k[(V_{GS}-V_{Th})V_{DS}-\frac{V_{DS}^2}{2}]=2*10^{-3}[7V_{D}-\frac{V_{D}^2}{2}]](/forum/latexrender/pictures/bbbec30c7e4d9a15fff853539bcedc61.png)

con

con

Sostituendo questo valore di

nell'espressione di

nell'espressione di  , segue:

, segue:

Cioè escono valori complessi e non posso ricavare l'espressione di

.

.Quindi? dove sbaglio?

;

;  perché ai capi di R1 vi è una caduta di potenziale di 1 V;

perché ai capi di R1 vi è una caduta di potenziale di 1 V;

, pertanto dalla relazione precedente si ricava

, pertanto dalla relazione precedente si ricava  e quindi

e quindi  .

. , perché altrimenti non verrebbe rispettata la condizione di accensione del transistor.

, perché altrimenti non verrebbe rispettata la condizione di accensione del transistor. .

. , è già di per sé un assurdo.

, è già di per sé un assurdo. ;

;  ;

;  quindi il transistor è polarizzato al limite della zona di saturazione.

quindi il transistor è polarizzato al limite della zona di saturazione.