Dimensionamento PMOS in logica PSEUDO NMOS

Salve,

dovrei dimensionare il rapporto W del seguente PMOS.

Ho già la soluzione, ma sinceramente non l'ho compresa.

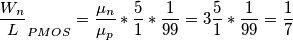

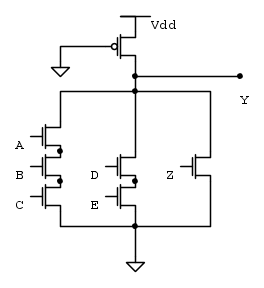

Ecco il circuito:

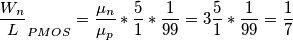

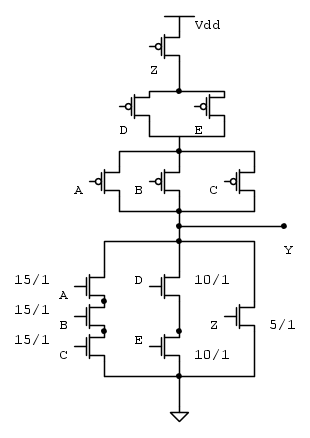

con

e

la soluzione è

ma da dove sbuca quel 1/99? cosa è?

dovrei dimensionare il rapporto W del seguente PMOS.

Ho già la soluzione, ma sinceramente non l'ho compresa.

Ecco il circuito:

con

e

la soluzione è

ma da dove sbuca quel 1/99? cosa è?

per i Pmos devi tenere conto che

per i Pmos devi tenere conto che