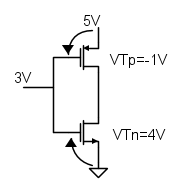

Tensioni di soglia in invertitore CMOS.

Ciao a tutti. La settimana scorsa ho sostenuto un colloquio, nel quale mi è stato chiesto di esporre le conoscenze sul MOS. Ho iniziato con l'invertitore CMOS, specificando il suo uso nell'elettronica DIGITALE. Ho disegnato l'invertitore CMOS, ho spiegato il funzionamento dicendo che le soglie dell'NMOS e del PMOS erano uguali in modulo. Sinceramente non ricordavo esattamente il motivo, ma ricordavo che era cosi. L'intervistatore mi ha detto che i due MOS non hanno le soglie uguali, altrimenti non funziona nulla. Tornando a casa, ho controllato vari riferimenti, tra cui il libro usato all'uni (Rabaey) e ho visto che le soglie sono uguali per massimizzare i margini di rumore (sfortunatamente non ho trovato la matematica/fisica che ci sta dietro, per cui l'affermazione mi è rimasta un po' appesa...). Quindi ho ipotizzato le seguenti cose:

1) l'intervistatore si è sbagliato

2) l'intervistatore si riferiva a qualche altra applicazione (analogica?), ma questo presuppone che non abbia ascoltato quando io ho detto l'uso in elettronica digitale dell'inverter CMOS

3) l'intervistatore ha volontariamente fatto un affermazione sbagliata per vedere se ero preparato per ribattere e difendere la mia affermazione.

Aldilà della motivazione, mi interesserebbe sapere le implicazioni, visto che come dicevo non ho trovato delle speigazioni esaurienti. Io ho ipotizzato che se le soglie non sono uguali in modulo, durante la transizione tra uno stato e l'altro entrambi i MOS sono spenti e il nodo di uscita si troverà in uno stato floating, più suscettibile quindi ad accoppiamenti capacitivi e altri disturbi (crosstalk ecc). L'intervistatore mi ha chiesto cosa succede in questa fase di transizione, io gli ho detto correttamente che il nodo è floating ma non ho proseguito con il ragionamento (fatto poi a mente fredda a casa), forse si aspettava la prosecuzione del ragionamento, per poi confermare quindi che la mia affermazione iniziale era corretta; questo magari avvalora l'ipotesi (3).

Secondo voi è quello il motivo per cui le tensioni di soglia sono uguali in modulo? O c'è altro?

1) l'intervistatore si è sbagliato

2) l'intervistatore si riferiva a qualche altra applicazione (analogica?), ma questo presuppone che non abbia ascoltato quando io ho detto l'uso in elettronica digitale dell'inverter CMOS

3) l'intervistatore ha volontariamente fatto un affermazione sbagliata per vedere se ero preparato per ribattere e difendere la mia affermazione.

Aldilà della motivazione, mi interesserebbe sapere le implicazioni, visto che come dicevo non ho trovato delle speigazioni esaurienti. Io ho ipotizzato che se le soglie non sono uguali in modulo, durante la transizione tra uno stato e l'altro entrambi i MOS sono spenti e il nodo di uscita si troverà in uno stato floating, più suscettibile quindi ad accoppiamenti capacitivi e altri disturbi (crosstalk ecc). L'intervistatore mi ha chiesto cosa succede in questa fase di transizione, io gli ho detto correttamente che il nodo è floating ma non ho proseguito con il ragionamento (fatto poi a mente fredda a casa), forse si aspettava la prosecuzione del ragionamento, per poi confermare quindi che la mia affermazione iniziale era corretta; questo magari avvalora l'ipotesi (3).

Secondo voi è quello il motivo per cui le tensioni di soglia sono uguali in modulo? O c'è altro?