Capacità intrinseca mosfet

Salve,

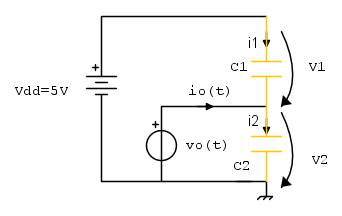

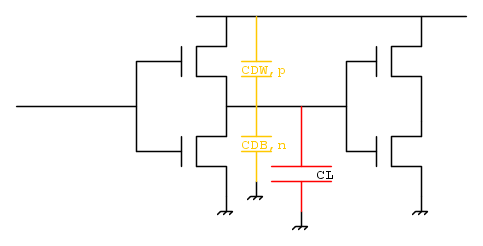

stavo studiando l'inverter CMOS fino a quando mi sono imbattuto nell'analisi del tempo di ritardo. Per far ciò sono state introdotte varie capacità intrinseche del PMOS e NMOS che poi sono state rappresentate mediante una capacità CL. Il libro per semplicità considera solo la capacità di gate e di drain. Il circuito in analisi è il seguente:

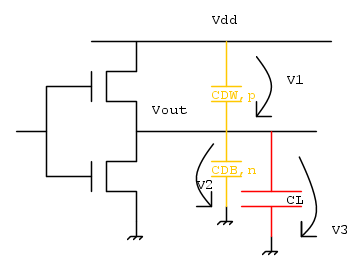

Nei vari passaggi per il calcolo di CL arriva a dire che la capacità CDW,p è in parallelo con CL ed è proprio questo che mi sfugge. Dato che CL e CDW,p hanno un punto a tensione comune e CL collegata a massa mentre CDW,p è collegata alla tensione di alimentazione come è possibile che siano in parallelo, ergo hanno applicata la stessa tensione?

stavo studiando l'inverter CMOS fino a quando mi sono imbattuto nell'analisi del tempo di ritardo. Per far ciò sono state introdotte varie capacità intrinseche del PMOS e NMOS che poi sono state rappresentate mediante una capacità CL. Il libro per semplicità considera solo la capacità di gate e di drain. Il circuito in analisi è il seguente:

Nei vari passaggi per il calcolo di CL arriva a dire che la capacità CDW,p è in parallelo con CL ed è proprio questo che mi sfugge. Dato che CL e CDW,p hanno un punto a tensione comune e CL collegata a massa mentre CDW,p è collegata alla tensione di alimentazione come è possibile che siano in parallelo, ergo hanno applicata la stessa tensione?

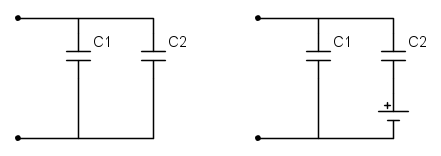

): se una armatura di una capacita` e` collegata a un potenziale fisso, la puoi collegare a qualunque altro potenziale fisso, cambia solo il livello di continua sul condensatore, livello che non ha nessun effetto (*).

): se una armatura di una capacita` e` collegata a un potenziale fisso, la puoi collegare a qualunque altro potenziale fisso, cambia solo il livello di continua sul condensatore, livello che non ha nessun effetto (*).

) avrò che

) avrò che

e quindi sono in parallelo perché hanno la stessa tensione.

e quindi sono in parallelo perché hanno la stessa tensione.  invece ha valore

invece ha valore  quindi la tensione è diversa. A questo punto forse sbaglio a dire che a due componenti elettrici collegati in parallelo è applicata la stessa tensione perché sennò non capisco in cosa stia sbagliando.

quindi la tensione è diversa. A questo punto forse sbaglio a dire che a due componenti elettrici collegati in parallelo è applicata la stessa tensione perché sennò non capisco in cosa stia sbagliando.