Progettare porta logica CMOS

Salve ragazzi,ho un piccolo dubbio riguardante tale traccia.

Disegnare lo schema circuitale di una porta logica CMOS che implementi la funzione: Y=(AB+C)D+E (TUTTO NEGATO).

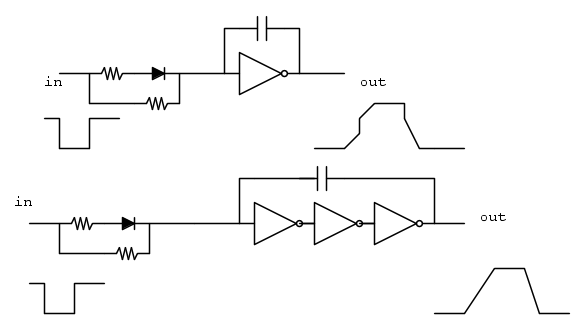

E' possibile dimensionare i transitori in modo che la transizione basso-alto dell'uscita sia 2 volte più lenta di quella alto-basso senza alternare i livelli logici?

Ho fatto il primo punto ,il mio dubbio è sul secondo. Qualcuno può aiutarmi?

Ringrazio anticipatamente

Disegnare lo schema circuitale di una porta logica CMOS che implementi la funzione: Y=(AB+C)D+E (TUTTO NEGATO).

E' possibile dimensionare i transitori in modo che la transizione basso-alto dell'uscita sia 2 volte più lenta di quella alto-basso senza alternare i livelli logici?

Ho fatto il primo punto ,il mio dubbio è sul secondo. Qualcuno può aiutarmi?

Ringrazio anticipatamente