Per quanto riguarda il dimensionamento, lascio la parola ad altri... per il

design del circuito, puoi seguire delle semplici "regolette":

1 - Guarda i

nMOS come interruttori: in stato alto (1) sono dei corto circuiti, in stato basso (0) dei circuiti aperti. Per i

pMOS, puoi ragionare dualmente (ma di fatto, come vedrai dalle regole successive, per disegnare il circuito non ti servirà ri-analizzare la parte pMOS: sfrutteremo la proprietà di dualità per semplificare le cose)

2 - Per disegnare la parte nMOS:

- Se hai un AND, metti i transistor in serie (la "catena" di transistor condurrà solo se tutti saranno in stato 1, ottenendo di fatto "l'equivalente" di una funzione AND)

- Se hai un OR, metti i transistor in parallelo (stesso ragionamento appena visto per AND)

3 - Per disegnare la parte pMOS, trasforma le serie nMOS in paralleli e i paralleli nMOS in serie

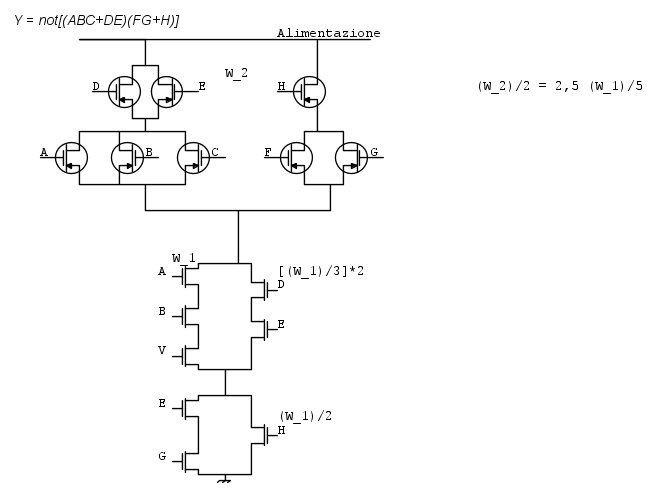

Facciamo insieme l'esercizio che hai proposto (ricordando che le porte logiche costruite saranno in logica negativa, e quindi potremo "non curarci" del NOT che "grava" sulla nostra funzione logica):

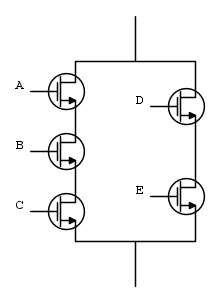

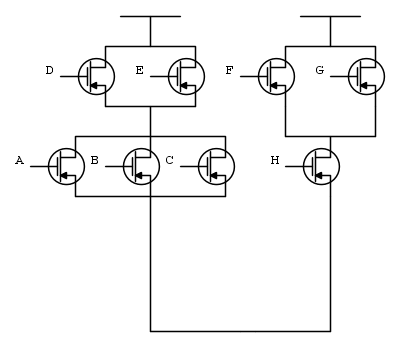

-> Prima parentesi: ABC + DE. Ovvero, A in serie a B in serie a C, tutto in parallelo alla serie di D ed E.

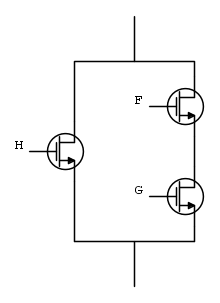

-> Seconda parentesi: FG+H. Ragionando come sopra, abbiamo H in parallelo alla serie di F e G.

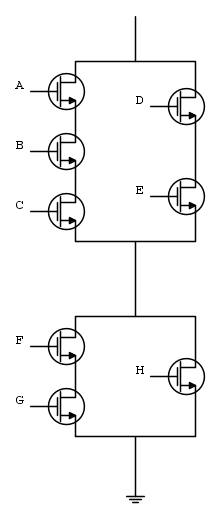

-> Uniamo le due parentesi: tra di loro c'è un AND. Dobbiamo pertanto mettere in serie i due circuiti ricavati.

-> Sviluppiamo la parte pMOS: come abbiamo visto sopra, basta trasformare le serie in paralleli e viceversa.

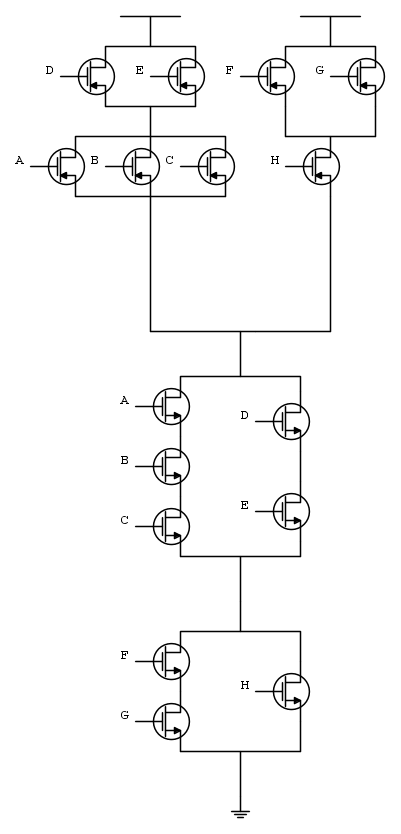

-> Uniamo le due parti, e otteniamo il circuito che volevamo: