Partiamo da un presupposto: DIMENTICA TUTTO QUELLO CHE HAI LETTO SU INTERNET. Si studia sui libri, non su siti web dove chi sa chi scrive ciò che gli gira per la testa.

Detto questo, andiamo avanti... per poterti rispondere, occorre determinare un dettaglio non indifferente: tu hai idea di cosa sia una macchina a stati finiti? Nel dubbio, te lo spiego io:

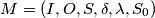

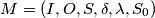

Una

macchina a stati finiti deterministica è il modello matematico di un "computer limitatamente potente" (diciamo così, giusto per capirci), ed è definita, nell'ambito del progetto dei sistemi digitali, in una forma detta

transductor form (o

transducer form, fa lo stesso): una sestupla

dove

è l'alfabeto d'ingresso,

è l'alfabeto d'uscita,

è l'insieme degli stati,

è la funzione di transizione dello stato,

è la funzione che determina il valore dell'uscita e

è l'insieme degli stati iniziali della macchina. Se

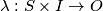

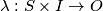

dipende solo dallo stato corrente, ovvero

, la macchina a stati finiti è una

macchina di Moore; se invece

dipende anche dall'ingresso, ovvero

, la macchina a stati finiti è una

macchina di Mealy.

Perché queste definizioni sono importanti? Innanzitutto, perché operare con entità che non si conoscono è una cretinata, e secondariamente perché la definizione della funzione di transizione dello stato risponde a una tua domanda: se noti, essa ha come dominio il prodotto cartesiano dell'alfabeto d'ingresso e dell'insieme degli stati e come immagine l'insieme degli stati, ovvero associa uno stato successivo

ad ogni coppia ingresso-stato. In altri termini, la transizione da uno stato all'altro è determinata dallo stato presente e dal simbolo dell'alfabeto d'ingresso appena ricevuto.

Andiamo al tuo progetto: si tratta di un circuito logico, quindi sappiamo per certo che

e

.

ORA FERMIAMOCI.

Abbiamo ancora detto pochissimo del tuo progetto, ma già siamo giunti a un dettaglio importante: dato l'alfabeto di input, possiamo determinare la risposta ad una delle tue domande: le condizioni di transizione da uno stato all'altro saranno, dato per assodato lo stato in cui si trova la FSM, nella forma

input = 0 o

input = 1, perché il nostro alfabeto include solo quei due simboli, e dunque non ci aspettiamo che il nostro input abbia un altro valore.

Ora, valutiamo un attimo cosa deve fare il tuo circuito... io non ho capito una sillaba della tua specifica, la quale è redatta in una lingua che - permettimi di dirtelo - somiglia solo vagamente all'italiano, quindi me la "invento": poniamo che il tuo circuito debba buttar fuori un 1 ogni volta che riconosce una sequenza 111 o 100, e poi resettarsi in attesa di una nuova sequenza. Con questa specifica, il circuito opera sostanzialmente così:

- Stato 0, attesa dell'ingresso: se arriva un 1, allora sta iniziando una sequenza che potrebbe interessarci e quindi ci spostiamo allo stato 1, mentre se arriva uno 0 non ce ne frega niente e quindi possiamo rimanere in attesa.

- Stato 1, attendiamo l'input: se è uno 0, potremmo essere in presenza della seconda sequenza che ci interessa, quindi spostiamoci allo stato 2; se è un 1, potremmo essere in presenza della prima sequenza, quindi ci spostiamo allo stato 3.

- Stato 2, attendiamo l'input: se è un 1, non abbiamo completato la sequenza e torniamo allo stato 1 (NON allo stato 0, attenzione: non abbiamo completato la sequenza, ma l'ultimo input ricevuto è comunque un 1, quindi la sequenza potrebbe iniziare ora!); se è uno 0, siamo assolutamente in presenza della seconda sequenza di interesse, quindi andiamo allo stato 4 e mettiamo in output un 1.

- Stato 3, attendiamo l'input: se è un 1, siamo in presenza della prima sequenza, dunque andiamo allo stato 4 e mettiamo in output un 1; se è uno 0, non siamo in presenza di alcuna sequenza utile, quindi torniamo allo stato 0.

- Stato 4: abbiamo ottenuto una sequenza di interesse, quindi torniamo allo stato 0. Scartiamo l'input ricevuto in questo stato (se fai una cosa del genere in un circuito reale potenzialmente ti rendi passibile di violenza fisica... ma è tardi e sono stanco, quindi tagliamo corto e facciamo così).

Tutto 'sto discorso può essere rappresentato da questo diagramma (sono le due di notte... spero di averlo fatto bene):

Come vedi, di tutti quei trip assurdi che ti stavi facendo non c'è traccia... alcuni di essi hanno un fondamento reale, ma per ora lasciamoli stare: in questa prima fase, cerca di capire le (tante) cose che abbiamo appena visto, poi pensiamo al resto.

Ora, un ultimo dettaglio e poi me ne vado a letto: quella che ti ho proposto è una FSM che rappresenta la nostra specifica... ma non

l'unica FSM: progettisti differenti potrebbero tirar fuori automi differenti. Giusto per farti un esempio: lo stato 4 non ci serve, quindi potremmo eliminarlo e far "ritornare" gli stati 2 e 3 allo stato 0, così:

Inutile dire che questo design è decisamente migliore: ha uno stato in meno, e soprattutto non si mangia l'input quando conclude la sequenza.

dove

dove  è l'alfabeto d'ingresso,

è l'alfabeto d'ingresso,  è l'alfabeto d'uscita,

è l'alfabeto d'uscita,  è l'insieme degli stati,

è l'insieme degli stati,  è la funzione di transizione dello stato,

è la funzione di transizione dello stato,  è la funzione che determina il valore dell'uscita e

è la funzione che determina il valore dell'uscita e  è l'insieme degli stati iniziali della macchina. Se

è l'insieme degli stati iniziali della macchina. Se  , la macchina a stati finiti è una

, la macchina a stati finiti è una  , la macchina a stati finiti è una

, la macchina a stati finiti è una  e

e  .

.