Problema generatori PWL e PULSE

Inviato: 21 ott 2012, 10:31

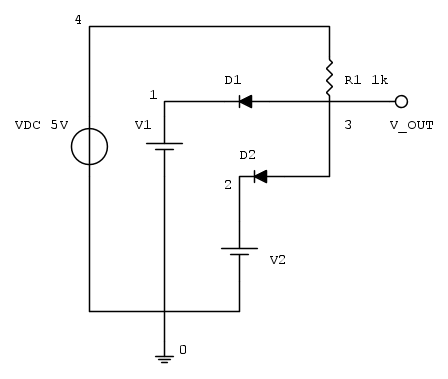

Ragazzi avrei un problema con questi due tipi di generatori. Consideriamo il seguente circuito:

La seguente netlist con generatori lineari a tratti per vedere l'andamento della risposta al variare della tensione dei due generatori:

Graficamente:

La linea rossa corrisponde a V1, la linea verde a V2, la linea gialla a V_OUT.

In corrispondenza di 2s in uscita dovrei avere circa 0.7V (livello logico basso) invece mi ritrovo, seppur per un periodo di tempo piccolo, un picco ti tensione quando dovrei avere una linea orizzontale in corrispondenza di 0.7V fino a 3V quando entrambi i diodi si interdiscono contemporaneamente determinando in uscita VDC, quindi 5V (livello logico alto)..

La seguente netlist con generatori lineari a tratti per vedere l'andamento della risposta al variare della tensione dei due generatori:

Codice: Seleziona tutto

*porta logica AND

.lib "./elettronica_digitale.lib"

VDC 4 0 DC 5

D1 3 1 D1N4148

D2 3 2 D1N4148

R1 3 4 1k

V1 1 0 PWL(0 0 1.99 0 2.01 5 3.99 5 4.01 0)

V2 2 0 PWL(0 0 0.99 0 1.01 5 1.99 5 2.01 0 2.99 0 3.01 5 3.99 5 4.01 0)

.TRAN 1m 4

.PROBE

.ENDGraficamente:

La linea rossa corrisponde a V1, la linea verde a V2, la linea gialla a V_OUT.

In corrispondenza di 2s in uscita dovrei avere circa 0.7V (livello logico basso) invece mi ritrovo, seppur per un periodo di tempo piccolo, un picco ti tensione quando dovrei avere una linea orizzontale in corrispondenza di 0.7V fino a 3V quando entrambi i diodi si interdiscono contemporaneamente determinando in uscita VDC, quindi 5V (livello logico alto)..