Ridurre I/O digitali su LM3S9B96 della Texas

Buongiorno a tutti,

oggi vengo a porvi un quesito semplice semplice (che quasi mi vergogno )

)

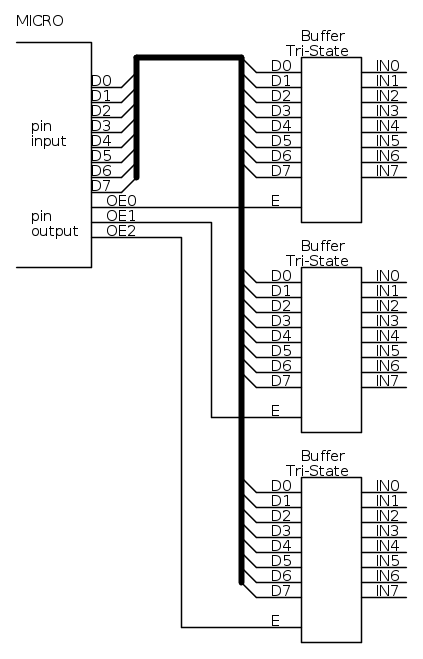

Ho necessità di gestire un consistente numero di I/O digitali (tastiere, tasti di cloches) con un microcontrollore.

Il poverino ha già parecchie altre mansioni da eseguire, per cui il numero di pin rimasti inizia ad essere esiguo e vorrei trovare un modo più intelligente per gestire tutti questi I/O.

La prima cosa che mi è venuta in mente è stata inserire un integrato che faccia la codifica di questi input.

Ad esempio, supponendo di avere 8 bit in input, in teoria basterebbero 3 bit in uscita per dirmi quale è intervenuto (in realtà ne servono 4 per sapere quando nessuno interviene).

Questo è sicuramente possibile, ma si viene a verificare il problema di non poter conoscere le situazioni in cui più input sono intervenuti contemporaneamente (a meno che mi accontenti di una certa latenza, magari con un clock bello rapido.. potrebbe essere un'ipotesi).

Al che ho pensato piuttosto che potrebbe essere utile invece serializzare gli N input che intervengono, anche qui con un clock bello rapido che mi garantisca una risposta accettabile (chiaramente se premo dei pulsanti non voglio vedere l'effetto dopo mezz'ora...)

Sapete darmi qualche consiglio? Magari da inesperto esiste qualcosa di più furbo da adoperare.

Grazie :)

oggi vengo a porvi un quesito semplice semplice (che quasi mi vergogno

Ho necessità di gestire un consistente numero di I/O digitali (tastiere, tasti di cloches) con un microcontrollore.

Il poverino ha già parecchie altre mansioni da eseguire, per cui il numero di pin rimasti inizia ad essere esiguo e vorrei trovare un modo più intelligente per gestire tutti questi I/O.

La prima cosa che mi è venuta in mente è stata inserire un integrato che faccia la codifica di questi input.

Ad esempio, supponendo di avere 8 bit in input, in teoria basterebbero 3 bit in uscita per dirmi quale è intervenuto (in realtà ne servono 4 per sapere quando nessuno interviene).

Questo è sicuramente possibile, ma si viene a verificare il problema di non poter conoscere le situazioni in cui più input sono intervenuti contemporaneamente (a meno che mi accontenti di una certa latenza, magari con un clock bello rapido.. potrebbe essere un'ipotesi).

Al che ho pensato piuttosto che potrebbe essere utile invece serializzare gli N input che intervengono, anche qui con un clock bello rapido che mi garantisca una risposta accettabile (chiaramente se premo dei pulsanti non voglio vedere l'effetto dopo mezz'ora...)

Sapete darmi qualche consiglio? Magari da inesperto esiste qualcosa di più furbo da adoperare.

Grazie :)