Impedenza digital output

Inviato:

20 gen 2026, 8:29da EcoTan

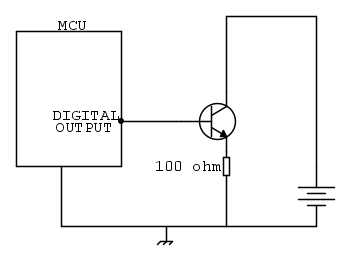

Se prendiamo questo schemino di principio:

e supponiamo che la MCU abbia 3,3V di alimentazione e la sua "Maximum current sourced/sunk by any I/O pin" sia 8 mA, il circuito può dirsi corretto?

Il mio dubbio è che considerando la giunzione base-emettitore di un transistor generico come una capacità, credo 100-200 pF, la corrente iniziale sul fronte OFF-ON potrebbe superare il valore consentito.

O invece quella capacità è dovuta principalmente all'effetto Miller cioè non si presenta in quanto non vi è amplificazione di tensione? E quindi quel circuito va bene?

Re: Impedenza digital output

Inviato:

20 gen 2026, 9:27da lelerelele

bella domanda.

considerando che ho anche un minimo ritardo di conduzione sulla corrente di collettore, potrei avere problemi, e come dicevi tu, la capacità di base a sua volta puo darne, mi pare che la capacità tra BE sia minima, mentre sia massima la capacità tra BC, in questo caso la tensione in BC varia di 3.3V, non fara gran danni.

Se dovessi farlo io valuterei principalmente se ho una elevata transizione degli stati, perché il danno credo sia principamente dovuto a dissipazione, per lo stadio di uscita della MCU, a basse commutazioni non mi farei grandi problemi, (magari sbagliando), poi testerà il tutto.....

non ho mai usato un inseguitore, anche perché mi trovo un'uscita molto bassa di tensione, ed evito tutti quei problemi.

saluti.

Re: Impedenza digital output

Inviato:

20 gen 2026, 11:33da Etemenanki

Mettiamola da un altro punto di vista ... la giiunzione BE di un BJT e' l'equivalente di un diodo, cosa succede alla corrente in uscita dal pin della MCU dopo che la soglia BE (0.6 / 0.7 V) e' stata superata, e la tensione di uscita dal pin cerca di arrivare a 3.3V, chiudendone quindi brutalmente circa 2.6 verso GND ?

Dice il saggio: "MAI pilotare transistor senza resistenza di base"

Re: Impedenza digital output

Inviato:

20 gen 2026, 11:43da gvee

Se non metti la R di base, hai un corto diretto con la alimentazione attraverso il PMOS (Digital output) di uscita.

Gli 8mA sono per dissipazione di potenza. Ossia che per correnti superiori si può bruciare il MOS corrispondente, quindi il pin..

Re: Impedenza digital output

Inviato:

20 gen 2026, 14:12da gvee

gvee ha scritto:Se non metti la R di base, hai un corto diretto con la alimentazione attraverso il PMOS (Digital output) di uscita.

Non avevo fatto caso alla R da 100 ohm.

Re: Impedenza digital output

Inviato:

20 gen 2026, 15:33da Etemenanki

Fa niente, senza resistenza di base non andrebbe mai fatto, per principio.

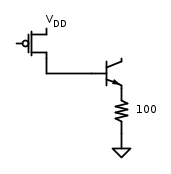

E poi un carico in open collector va messo sul collettore, non fra emettitore e GND.

Re: Impedenza digital output

Inviato:

20 gen 2026, 15:48da GioArca67

Ma il dato di corrente massima all'uscita (gli 8mA) sono massimi assoluti o massimi ...mediamente?

Re: Impedenza digital output

Inviato:

20 gen 2026, 16:04da MarcoD

Ma il dato di corrente massima all'uscita (gli 8mA) sono massimi assoluti o massimi ...mediamente?

bunoa domanda.

Se ben ricordo,mi pare che le uscite digitali dell'ATMEGA168 possono sopportare un cortocircuito permanente, limitando la corrente a 40 mA. Ma potrei sbagliarmi.

(Failure Mode Criticality Analysis ) E' credibile che il carico di 100 ohm possa venire messo in cortocircuito? Nel caso di corto, occorre proteggere l'uscita della MCU da un danneggiamento ?

E' credibile che il transistor abbia un hfe minimo = 50 ?

Re: Impedenza digital output

Inviato:

20 gen 2026, 16:16da GioArca67

Una Rb da 330 ohm la metterei comunque, certo se ci sono esigenze di minimalità dei componenti...

Re: Impedenza digital output

Inviato:

20 gen 2026, 16:42da gvee

Etemenanki ha scritto:E poi un carico in open collector va messo sul collettore, non fra emettitore e GND.

Era per mostrare il path e non rifare un disegno, non per disegnare un open collector.