Purtroppo gli algoritmi di sostituzione e le politiche di scrittura non sono gli unici parametri che caratterizzano un'architettura di cache.

Lo schema che hai linkato non è abbastanza informativo per capire com'è strutturato il sistema di memoria, e quindi analizzare in dettaglio come avviene la comunicazione tra cpu e main memory. Da esso possiamo solo capire il numero di cache e a cosa sono destinate.

Ci sono tre livelli per i dati e uno per le istruzioni, anche se non capisco perché la cache istruzioni non è collegata al bus di sistema o ad un livello di cache superiore. Comunque quello schema non mi piace proprio.

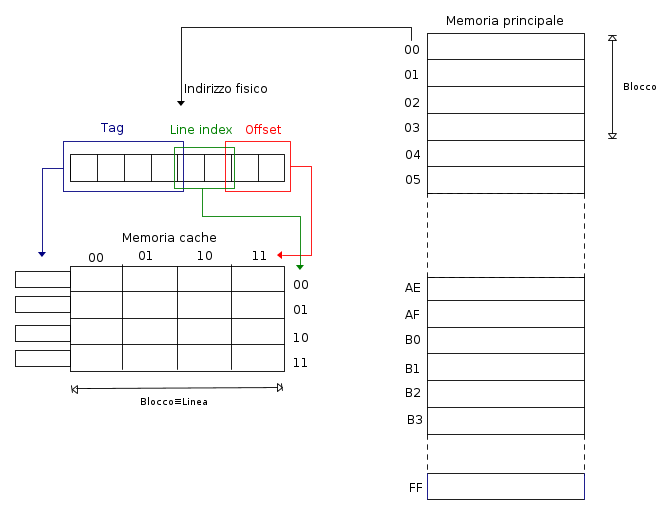

Per capirci ti faccio un esempio semplificato: il sistema è composto da un livello di cache completamente associativa di 16 B e da una memoria primaria di 256 B. La memoria è indirizzabile al singolo byte ed è divisa in blocchi di 4 B.

Assumiamo che sia una cache istruzioni.

Ora fregandocene di quale sia il programma in esecuzione, di quali istruzioni sia composto, di come si incrementa il program counter e del senso della vita! Ipotizziamo che il flusso di programma richieda il caricamento delle istruzioni contenute nei seguenti indirizzi di primaria espressi in esadecimale:

01

02

03

04

A3

A4

A5

A6

06

07

La cpu richiede la prima istruzione del programma, contenuta in

. Ma essendo la cache inizialmente vuota il sistema va subito a cercarla in memoria primaria, caricando l'intero blocco contenente l'indirizzo richiesto in cache.

L'indirizzo fisico è quindi:

, i due bit di line index sono entrambi a zero, quindi questa locazione di memoria si può trovare solo nella prima linea della cache (00). Per cui il blocco viene caricato nella prima linea di cache ed etichettata con il tag

.

Le successive due istruzioni fanno parte dello stesso blocco, quindi la cpu le troverà gia in cache.

L'istruzione allocata in

ha line index

, quindi deve essere memorizzata nella seconda linea di cache (01).

Ora tocca all'istruzione salvata in

, ha i bit di line index

quindi va salvata nella prima linea di cache, rimpiazzando il blocco precedentemente allocato.

etc etc

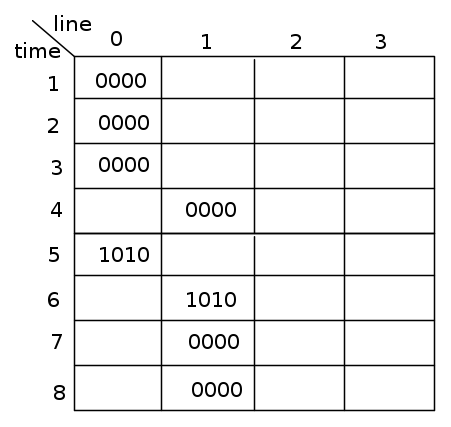

Segue una mappa, che descrive l'evoluzione temporale della cache. Nelle caselle identificate dalle coordinate: tempi/linea; ci sono i tag.

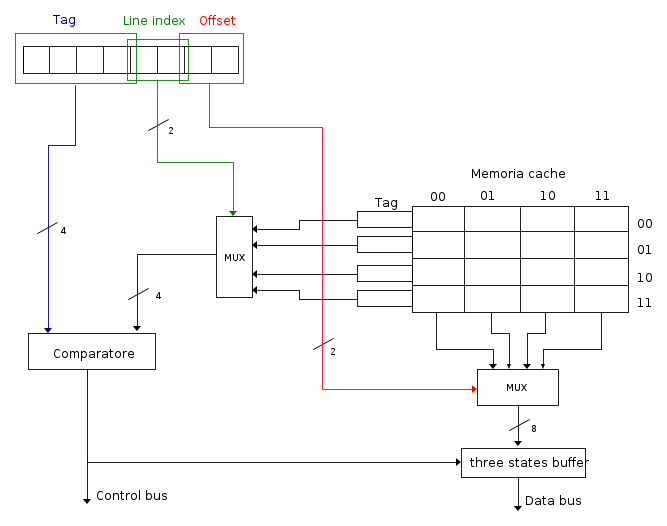

Inoltre ti posto anche uno schema un po meno di principio che può aiutare a chiarire l'architettura del sistema.

Naturalmente l'indirizzamento diretto è una delle tecniche più rozze, per avere una buona panoramica ti consiglio di leggere il capitolo tre di

Architettura e organizzazione dei calcolatori. Progetto e prestazioni, poi se vuoi approfondire puoi leggere le innumerevoli pubblicazioni la citate.

Dante

. Ma essendo la cache inizialmente vuota il sistema va subito a cercarla in memoria primaria, caricando l'intero blocco contenente l'indirizzo richiesto in cache.

. Ma essendo la cache inizialmente vuota il sistema va subito a cercarla in memoria primaria, caricando l'intero blocco contenente l'indirizzo richiesto in cache.  , i due bit di line index sono entrambi a zero, quindi questa locazione di memoria si può trovare solo nella prima linea della cache (00). Per cui il blocco viene caricato nella prima linea di cache ed etichettata con il tag

, i due bit di line index sono entrambi a zero, quindi questa locazione di memoria si può trovare solo nella prima linea della cache (00). Per cui il blocco viene caricato nella prima linea di cache ed etichettata con il tag  .

.  ha line index

ha line index  , quindi deve essere memorizzata nella seconda linea di cache (01).

, quindi deve essere memorizzata nella seconda linea di cache (01). , ha i bit di line index

, ha i bit di line index  quindi va salvata nella prima linea di cache, rimpiazzando il blocco precedentemente allocato.

quindi va salvata nella prima linea di cache, rimpiazzando il blocco precedentemente allocato.