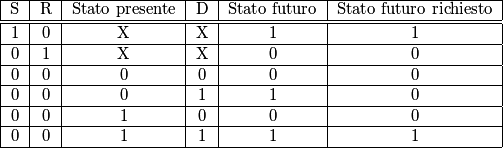

...e per quanto riguarda la sintesi della macchina a stati finiti via FF di tipo D, basta ricordare che (dalla tabella di eccitazione associata allo stesso), il suo ingresso D "copia" semplicemente lo stato futuro.

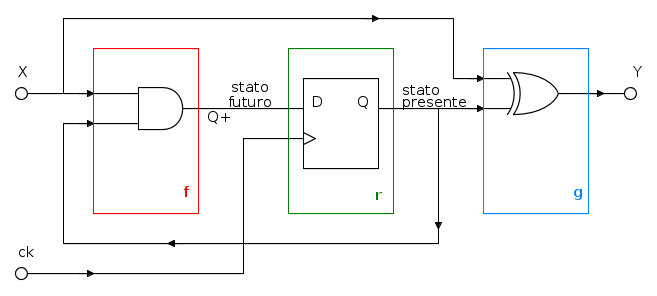

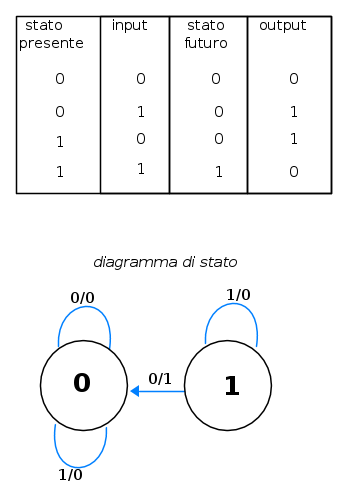

Ne segue che, dalla semplice ispezione della descrizione iniziale, l'ingresso D del FF sarà ottenibile da una semplice porta AND fra ingresso X e stato Q, e sempre dalla stessa, senza scomodare Karnaugh, è evidente che per ottenere la funzione d'uscita basterà un semplice OR esclusivo fra X e Q.

A dire il vero è un'automa un po' "strano", specie se lo stato iniziale è quello 0, in quanto se partiamo da lì, nello stato 1 non ci si arriverà mai e l'uscita, copiando semplicemente l'ingresso, renderebbe completamente inutile l'uso di una macchina sequenziale, se invece partiamo da stato iniziale 1, la macchina un qualche senso l'avrebbe ... tutto da scoprire.

A mio parere, dare problemi di questo tipo, senza partire dalle specifiche funzionali reali che la FSM deve sintetizzare fa perdere la vera essenza della macchina sequenziale.

Max

Max