Buonasera a tutti, dopo mesi di inattività finalmente l'altro ieri ho ripreso in mano questo progetto e ho provato a testarlo per poterne poi fare lo stampato.

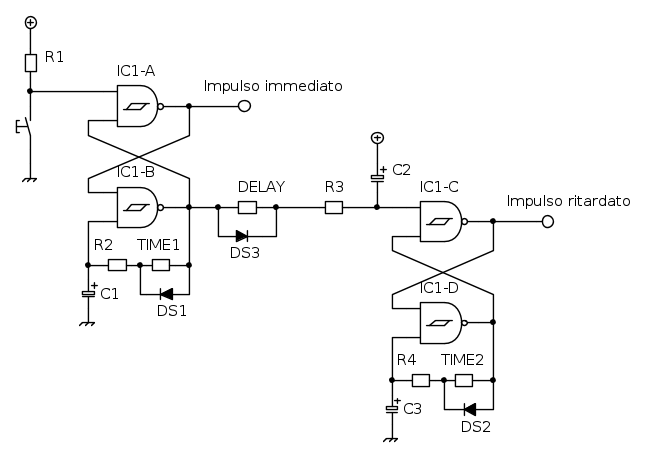

Ho riscontrato però un problema con l'ultimo schema del temporizzatore a CD4093. In sostanza, appena premo il pulsante l'uscita di IC1-A va a valore logico alto, mentre quella di IC1-B va a massa. Ciò permette al condensatore C2 di scaricarsi pian piano e quindi di attivare il secondo integrato non appena raggiunto un valore di soglia. Il problema è che non appena l'uscita di IC1-B torna alta (dovuta allo scaricarsi di C1 e quindi all'impostazione del RESET del latch) il condensatore C2 smette di scaricarsi e ricomincia a caricarsi. Se ho ad esempio impostato una durata di 10 secondi e un ritardo tra impulso immediato e ritardato di 9 secondi, idealmente dovrei avere:

OUT1 |----------|

OUT2 ---------|----------|

Ciò però presuppone di avere il valore logico dell'ingresso di IC1-C alto per i primi 9 secondi e successivamente basso (attivazione del SET del latch IC1-C) per i successivi 10.

In realtà nell'istante in cui si azzera l'uscita immediata (dopo 10 secondi) torna alta anche l'uscita di IC1-B, la quale fa ricaricare il condensatore che aveva appena iniziato a scaricarsi (a 9 secondi), e quindi non dà il tempo di mantenere attiva l'uscita ritardata. Cioè, detto in soldoni, la prima uscita rimane alta per 10 secondi e ok, la seconda si avvia dopo 9 secondi ma rimane attiva per, boh, 2 secondi a causa di questo problema. Inoltre tale uscita dipende fortemente dallo stato del condensatore, quindi a seconda dello stato precedente del condensatore l'uscita può restare attiva per 2 secondi se premo una volta il pulsante e, se lo ripremo immediatamente dopo, il condensatore parte non da Vcc, ma da un valore minore (poiché non ha avuto tempo di ricaricarsi fino al massimo), e ciò comporta che l'uscita si attiva prima (in quanto l'ingresso di IC1-C raggiunge il valore di soglia prima) e dura di più.

Ho provato a pensare a uno schema alternativo e mi è venuto questo:

Siccome una porta logica veniva lasciata inutilizzata, non serve neanche aggiungere altri integrati, basta aggiungere un potenziometro, una resistenza e un condensatore. Qui abbiamo due latch identici comandati all'accensione, il primo dal pulsante, il secondo dalla soglia raggiunta dalla scarica del condensatore. Il diodo DS3 garantisce che il condensatore torni allo stato iniziale di Vcc e quindi che due pressioni successive del pulsante non varino il ritardo. L'unica rogna è che abbiamo un nuovo potenziometro che, volendo fare le durate delle uscita uguali, dovrà essere sempre sincronizzato con il primo...

Con questa correzione il circuito temporizzatore con ritardo è preciso e tempo-invariante, e dopo aver fatto alcuni test non ho riscontrato alcun problema. Spero possa servire a qualcun altro prima o poi!

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)

.

. .

. ...

...