Progetto scolastico.

Moderatori: ![]() carloc,

carloc, ![]() g.schgor,

g.schgor, ![]() BrunoValente,

BrunoValente, ![]() IsidoroKZ

IsidoroKZ

0

voti

non avevo capito la parte degli ingressi liberi dell'integrato cosa dovevo fare!

0

voti

Gli ingressi li puoi collegare tanto a GND come a VDD, senza resistenza. Sono gli Output che in questo caso devi lasciare a vuoto. Se vuoi ti spiego il perché, più tardi perché tra 10m esco.

0

voti

da quanto ho capito perché maga gli ingressi possono creare delle interferenze con il circuito

0

voti

se lasciamo libere delle porte inutilizzate,queste possono creare dei seri problemi all'IC stesso sino a rischiare di danneggiarlo,non mi sembra una cosa cosi difficile da capire,devi accettarla cosi com'è

0

voti

eh ma scusa a scuola quando c'era da fare i progetti. nessuno metteva a massa le entrate rimanenti dell'integrato.

0

voti

Dunque, il perché non é bene lasciare gli ingressi flottanti é spiegato molto bene in questo post che sono andato a ripescare.

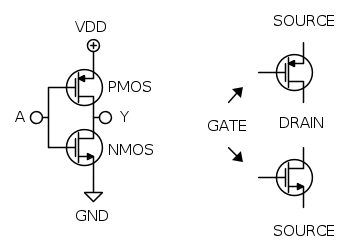

Ora, lo schema interno di un invertitore NOT CMOS, di base é questo:

Dove a fianco ho aggiunto pure i nomi dei morsetti dei MOS.

Dato che la resistenza di GATE di un MOSFET é altissima, (idealmente ), la resistenza di input non serve, basta collegarli a GND o a VDD.

), la resistenza di input non serve, basta collegarli a GND o a VDD.

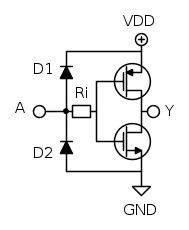

Tra l'altro i fabbricanti includono già le dovute protezioni e la resistenza di entrata così ad esempio.

così ad esempio.

Ma non serve tanto per limitare la corrente di entrata sennò per evitare auto oscillazioni etc, ma questo é un altro discorso.

Comunque, in qualsiasi caso, entrata a VDD o a GND, a circuito montato devi sempre fare attenzione agli output.

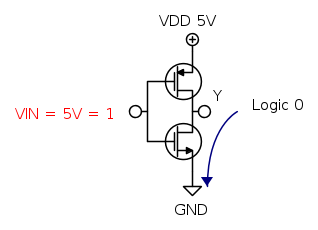

Nel caso di avere un 1 logico in entrata, o 5V per esempio

Il PMOS é spento quindi é come se fosse un interruttore aperto tra VDD e Y.

É pero l'NMOS ad essere acceso quindi si comporta come un interruttore chiuso tra Y e GND. Questo vuol dire che se accidentalmente crei un cortociruito tra VDD e Y, senza resistenza, idealmente rompi l'NMOS, realmente direi qualcosa di più perché passa tanta corrente, si scalda il componente e bruci il circuito interno.

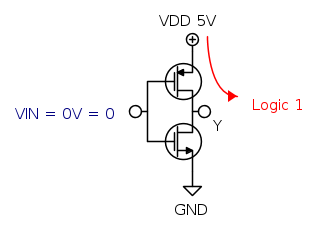

Invece quando hai sull'ingresso uno stato logico basso 0, o 0V

L'NMOS é spento ed il PMOS é acceso, quindi é quest'ultimo che si comporta come un interruttore chiuso tra VDD e Y, quindi se crei un cortocircuito accidentale tra Y e GND direi che rompi tutto.

Quindi, una volta montato il circuito fai una prova con il tester per vedere che non ci siano dei contatti che non ci devono essere, come appunto quelli citati.

La spiegazione é molto breve ma complicarla sarebbe inutile in questo momento, forse ti confonderebbe solo le idee e non voglio complicarti la situazione. Spero peró che nel suo piccolo ti aiuti a capire e magari ti invogli a studiare un po' di più o a voler capire perché quando l'entrata é a 1 é acceso l'NMOS e viceversa ... e tante altre cose, così come ho fatto io e tanti altri ragazzi.

Ora, lo schema interno di un invertitore NOT CMOS, di base é questo:

Dove a fianco ho aggiunto pure i nomi dei morsetti dei MOS.

Dato che la resistenza di GATE di un MOSFET é altissima, (idealmente

), la resistenza di input non serve, basta collegarli a GND o a VDD.

), la resistenza di input non serve, basta collegarli a GND o a VDD.Tra l'altro i fabbricanti includono già le dovute protezioni e la resistenza di entrata

così ad esempio.

così ad esempio.Ma non serve tanto per limitare la corrente di entrata sennò per evitare auto oscillazioni etc, ma questo é un altro discorso.

Comunque, in qualsiasi caso, entrata a VDD o a GND, a circuito montato devi sempre fare attenzione agli output.

Nel caso di avere un 1 logico in entrata, o 5V per esempio

Il PMOS é spento quindi é come se fosse un interruttore aperto tra VDD e Y.

É pero l'NMOS ad essere acceso quindi si comporta come un interruttore chiuso tra Y e GND. Questo vuol dire che se accidentalmente crei un cortociruito tra VDD e Y, senza resistenza, idealmente rompi l'NMOS, realmente direi qualcosa di più perché passa tanta corrente, si scalda il componente e bruci il circuito interno.

Invece quando hai sull'ingresso uno stato logico basso 0, o 0V

L'NMOS é spento ed il PMOS é acceso, quindi é quest'ultimo che si comporta come un interruttore chiuso tra VDD e Y, quindi se crei un cortocircuito accidentale tra Y e GND direi che rompi tutto.

Quindi, una volta montato il circuito fai una prova con il tester per vedere che non ci siano dei contatti che non ci devono essere, come appunto quelli citati.

La spiegazione é molto breve ma complicarla sarebbe inutile in questo momento, forse ti confonderebbe solo le idee e non voglio complicarti la situazione. Spero peró che nel suo piccolo ti aiuti a capire e magari ti invogli a studiare un po' di più o a voler capire perché quando l'entrata é a 1 é acceso l'NMOS e viceversa ... e tante altre cose, così come ho fatto io e tanti altri ragazzi.

Chi c’è in linea

Visitano il forum: Nessuno e 153 ospiti

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)