latch e macchine a stati?

Moderatori: ![]() carloc,

carloc, ![]() g.schgor,

g.schgor, ![]() BrunoValente,

BrunoValente, ![]() IsidoroKZ

IsidoroKZ

17 messaggi

• Pagina 1 di 2 • 1, 2

0

voti

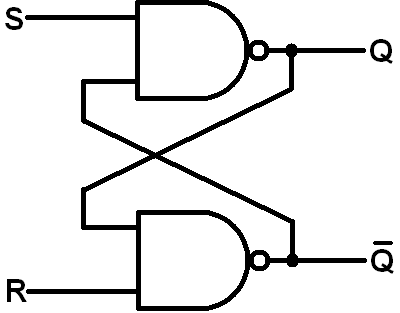

Non riesco a capire una cosa, mi ci sto chiudendo da gironi; il nostro prof ci ha detto che illatch non può essere utilizzato per le macchine a stati perché contiene al suo interno un circuito "rigenerativo" con 2 inverter; quando il clock è alto, lo stato quindi oscilla due volte e l'uscita dipende da quando tiro giù il clock; a me sinceramente non torna, i segnale prima di andare all'uscita passa per entrambi gli inverter, quindi l'uscita dovrebbe essere corretta

-

claudios96

claudios96

0 2 - Messaggi: 19

- Iscritto il: 28 giu 2016, 13:39

0

voti

Scusate non so perché non mi adatta l'immagine, sta a questo link http://i66.tinypic.com/ionqqf.jpg

-

claudios96

claudios96

0 2 - Messaggi: 19

- Iscritto il: 28 giu 2016, 13:39

0

voti

Immagina che a t=0, hai S=1 ed R=1. Se al tempo t=t1 entrambi gli ingressi commutano contemporaneamente ed hai S=0 ed R=0, che succede? Riesci a calcolare l'uscita?

0

voti

mm non riesco a ricollegare bene questo nello schema del nostro prof; R e S sappresentano E e D?

-

claudios96

claudios96

0 2 - Messaggi: 19

- Iscritto il: 28 giu 2016, 13:39

0

voti

il problema forse è che se il mio dato in ingresso cambia rapidamente, quindi prima è 0, poi 1, poi di nuovo 0 ecc. io non so quale valore memorizzo perché non so di preciso quando si abbassa il clock?E' l'unica cosa sensata che mi viene da pensare, perché il fatto degli inverter non lo capisco

-

claudios96

claudios96

0 2 - Messaggi: 19

- Iscritto il: 28 giu 2016, 13:39

1

voti

Secondo me invece c'è un problema a monte. Stai generalizzando attorno ad un problema specifico che hai omesso, o io non vedo.

La tua affermazione è generica o riferita a qualcosa di specifico?

La tua affermazione è generica o riferita a qualcosa di specifico?

-

Candy

Candy

32,5k 7 10 13 - CRU - Account cancellato su Richiesta utente

- Messaggi: 10123

- Iscritto il: 14 giu 2010, 22:54

0

voti

la mia domanda è perché il latch non può realizzare macchine a stati, il mio prof dice perché il segnale oscilla e io non ho capito perché oscilla, se perché il dato in ingresso può cambiare più volte o se perché il dato passa per i 2 inverter

-

claudios96

claudios96

0 2 - Messaggi: 19

- Iscritto il: 28 giu 2016, 13:39

0

voti

il latch come ce lo ha fatto il prof è in questo link qui http://i66.tinypic.com/ionqqf.jpg, purtroppo questo professore non ha un cavolo di libro di riferimento, ha fatto il corso alla lavagna, ogni volta sta a noi capire se ha sbagliato lui in classe o se ci sta una logica che non capiamo

-

claudios96

claudios96

0 2 - Messaggi: 19

- Iscritto il: 28 giu 2016, 13:39

0

voti

Quello nel disegno è una possibile implementazione a livello di MOS (ma non certo l'unica) di un D-latch.

perché dovrebbe oscillare?

A me risulta che si possano creare problemi di metastabilità e uscita "caotica" solo se il clock non rispetta il Tsetup e il Thold del dato.

perché dovrebbe oscillare?

A me risulta che si possano creare problemi di metastabilità e uscita "caotica" solo se il clock non rispetta il Tsetup e il Thold del dato.

-

Brianz

Brianz

5.828 5 10 - CRU - Account cancellato su Richiesta utente

- Messaggi: 858

- Iscritto il: 24 mar 2016, 11:27

17 messaggi

• Pagina 1 di 2 • 1, 2

Chi c’è in linea

Visitano il forum: Nessuno e 138 ospiti

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)