Ciao DoeM,

Grazie per la tua risposta.

Capisco che non è facile capire tutto.

Per la tua prima frase:

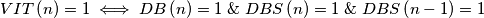

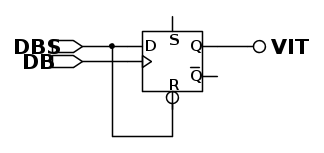

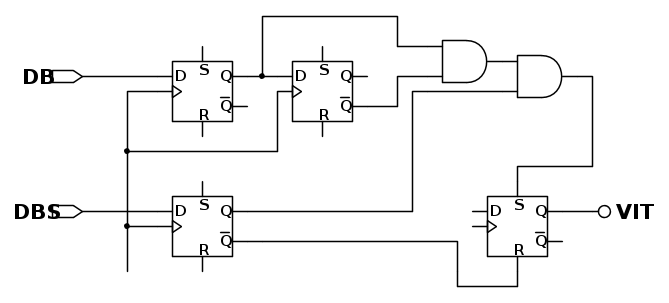

Se ho ben capito la questione, per resettare l'uscita allora sarebbe sufficiente collegare DB anche ad un ingresso di reset asincrono del flip-flop.

Ho provato a collegare DB a tutti gli ingressi ma c'è sempre una situazione che non funziona. Tu come la vedevi collegata ?

Per la seconda frase:

Sinceramente ho delle difficoltà a capire la struttura del sistema, ...

Allego un disegno che ti posso spiegare.

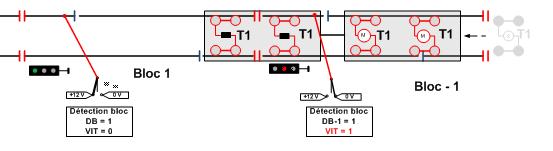

I trattini rossi sono le separazioni di tratto, i trattini blu sono le separazioni di rilevamento in un tratto, ce n'è sono due perché si puo andare in entrambe le direzioni.

Il rilevamento e un segnale di 12V, inviato da un elettronica (DB o DBS) che fa commutare un relè, da una locomotiva che arriva su un tratto (assorbimento di corrente). VIT è un segnale logico che è inviato a un elettronica che se VIT è a livello 0 (OV) il treno continuà a velocità normale, se invece VIT è a livello 1 (12V) fa commutare un relè che fa ralentare la locomotiva nel tratto grande e la ferma nel tratto piccolo.

Se facciamo un'equivalenza, DB corrisponde al rilevamento del tratto "Bloc-1" (B-1) e DBS corrisponde al rilevamento del tratto "Bloc 1" (B1). Lo si vede sul allegato.

1) Quindi nel mio caso, quando il treno T1 (composto di due locomotive) passa dal tratto B-1 al tratto B1, il sistema rileva che c'è un assorbimento di corrente al tratto B1 e invia l'informazione al tratto B-1 che fa ralentare e fermare il treno. Ma in questa situazione

non è normale (si vede nel allegato VIT = 1 in colore rosso perché è lo stesso treno che transita da B-1 a B1 (questo corrisponde alle linee T3 e T4 della mia tabella di verità).

2) Ma immaginando che T1 sta nella tratta B-1 e che si ferma, e mentre è fermo arriva un treno T2 sulla tratta B1 allora il sistema rileva che c'è un assorbimento di corrente al tratto B1 e invia l'informazione al tratto B-1 che fa ralentare e fermare il treno. In questa situazione

è normale (questo corrisponde alle linee T5 e T6 della mia tabella di verità) perché se il treno T1 vuol ripartire in direzione del tratto B1, non puo farlo perché c'è T2 che blocca il tratto. Nella medesima situazione, se T2 è gia fermo sulla tratta B1 e T1 arriva sulla tratta B-1 il treno T1 si deve inevitabilmente fermare (questo corrisponde alle linee T5 e T6 della mia tabella di verità)

Infine, per i due casi identici (T1 vuole andare da B-1 a B1) abbiamo un comportamento differente del sistema.

Speò essere stato abbastanza chiaro, non è facile da spiegare.

Grazie mielle ancora DoeM.

A presto... devo partire per andare a prendere il treno (quello verò

) perché vado a lavorare in treno.

- Détection_HOm_1.JPG (14.45 KiB) Osservato 5860 volte

Dario

,

,

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)

.

.