dbe8f ha scritto:Speò essere stato abbastanza chiaro, non è facile da spiegare.

Allora, mi pare di aver capito quasi tutto.

Solo un ultimo dubbio: come si capisce in che direzione si stanno muovendo i treni? Il sistema invia un valore di tensione diverso? Perché se non c'è modo di saperlo direttamente, mi sa che serve considerare almeno tre diversi blocchi, non due.

boiler ha scritto:Anche il primo è asincrono

E come tali io non ci farei affidamento.

KISS: Keep it strictly synchronous.

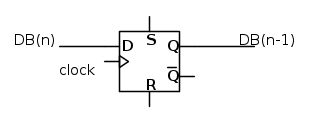

Certo che anche il primo è asincrono, ma quello è così palese che non ci ho tenuto a specificarlo. Sull'ingresso di clock

non è collegato un clock. E, come ho detto, non funziona.

Sul fatto di non fare affidamento su alcun circuito asincrono, sono totalmente in disaccordo: evitare logica asincrona è essenziale se si sta lavorando in domini di logica sincrona. Qua stiamo parlando di un plastico ferroviario, non di una FPGA. Non per niente, il motto KISS è nato nell'ambito dei progetti sincroni statici su CPLD/FPGA.

Non vedo perché ad un semaforo dovrebbe dare fastidio un ingresso asincrono (rispetto a quale clock poi? il semaforo ha un clock?).

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)