Ciao ragazzi, vorrei sapere se e come è possibile realizzare la funzione log in VHDL per implementazione su FPGA.

Il mio problema è che devo mandare in ingresso ad una FPGA dei segnali quantizzati in modo uniforme da matlab ma poi avrei bisogno di lavorare in dBm per il processing. In pratica avrei in ingresso i valori di tensione e dovrei lavorare in dBm per comodità, è possibile e conveniente una cosa del genere in VHDL?

Calcolo logaritmo in VHDL

Moderatore: ![]() jordan20

jordan20

11 messaggi

• Pagina 1 di 2 • 1, 2

0

voti

1

voti

Ciao,

per evitare complicazioni direi di spostare il problema a monte: puoi usare un amplificatore logaritmico con il seguente schema

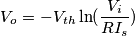

In questo circuito la relazione ingreso uscita è , dove

, dove  è la ben nota

è la ben nota  a temperatura ambiente e

a temperatura ambiente e  è la corrente di saturazione inversa del diodo. Potrebbe fare al caso tuo?

è la corrente di saturazione inversa del diodo. Potrebbe fare al caso tuo?

per evitare complicazioni direi di spostare il problema a monte: puoi usare un amplificatore logaritmico con il seguente schema

In questo circuito la relazione ingreso uscita è

, dove

, dove  è la ben nota

è la ben nota  a temperatura ambiente e

a temperatura ambiente e  è la corrente di saturazione inversa del diodo. Potrebbe fare al caso tuo?

è la corrente di saturazione inversa del diodo. Potrebbe fare al caso tuo?0

voti

La risposta dipende un po' dalle condizioni di contorno...

Potresti calcolare il logaritmo in base 2 semplicemente determinando quale è il bit piú a sinistra con valore 1. Questo ti dà un'approssimazione all'intero inferiore del logaritmo.

Devi poi prendere il resto è scalarlo in modo che vada sempre a finire in un intervallo definito e applicare una LUT.

A questo punto scalare il logaritmo di 2 al logaritmo che piú ti fa comodo è questione di una moltiplicazione.

Oppure, se il numero di bits non è eccessivo, vai di forza bruta e usa per tutto quanto una LUT.

C'è IEEE.math_real e potresti essere tentato di usarla

Va bene per calcolare per esempio i generics quando compili, ma non è sintetizzabile, quindi non fa al caso tuo.

Ciao Boiler

Potresti calcolare il logaritmo in base 2 semplicemente determinando quale è il bit piú a sinistra con valore 1. Questo ti dà un'approssimazione all'intero inferiore del logaritmo.

Devi poi prendere il resto è scalarlo in modo che vada sempre a finire in un intervallo definito e applicare una LUT.

A questo punto scalare il logaritmo di 2 al logaritmo che piú ti fa comodo è questione di una moltiplicazione.

Oppure, se il numero di bits non è eccessivo, vai di forza bruta e usa per tutto quanto una LUT.

C'è IEEE.math_real e potresti essere tentato di usarla

Va bene per calcolare per esempio i generics quando compili, ma non è sintetizzabile, quindi non fa al caso tuo.

Ciao Boiler

0

voti

il mio problema è proprio quello di passare da volt in dBm perché gli algoritmi a valle lavorano con i livelli in dB. L'amplificatore logaritmico è gia modellato a monte ma il problema principale è proprio la conversione volt dBm ma da come ho capito non è una soluzione ottimale.

PS: il numero di bit è 10/16 al max

PS: il numero di bit è 10/16 al max

0

voti

vediamo se ho capito quello che intendete:

io esco da matlab con i quanti segnale (1024 oppure 65536 livelli) poi genero un'array con i valori di conversione quanti dBm e li memorizzo in una tabella in memoria?

Non essendo molto pratico ancora di VHDL e FPGA non mi rendo conto se questi possano essere valori troppo elevati da memorizzare potreste darmi voi un parere; dovrei lavorare su una stratix 3 di Altera.

io esco da matlab con i quanti segnale (1024 oppure 65536 livelli) poi genero un'array con i valori di conversione quanti dBm e li memorizzo in una tabella in memoria?

Non essendo molto pratico ancora di VHDL e FPGA non mi rendo conto se questi possano essere valori troppo elevati da memorizzare potreste darmi voi un parere; dovrei lavorare su una stratix 3 di Altera.

0

voti

Ho sempre lavorato con Xilinx, non conosco le Altera Stratix, ma a naso direi che dovrebbe starci. Ad ogni modo lo vedi quando fai il build del tuo progetto, alla fine vedi le percentuali di risorse occupate sulla FPGA.

Non instanziare una RAM per poi caricarci i valori. Definiscili fissi nel tuo codice VHDL, in questo modo dai la possibilità al compiler di fare delle ottimizzazioni.

Usa un case-statement:

Questo è un esempio per il caso che il quanto abbia 10 bit.

Puoi togliere l'assegnazione per il caso others se sei sicuro di aver coperto tutti gli altri casi, altrimenti non sintetizzi correttamente!

Adatta i valori assegnati a quello che hai calcolato, compatibilmente con il tipo di DbmSignal.

Per non impestare il codice, metti il tutto in un processo, che infilerai in un'entità (io la chiamerei DbmConverter, o qualcosa del genere). Questa la instanzierai poi nel tuo codice principale come black-box e non dovrai piú curarti di quello che succede al suo interno.

Saluti Boiler

Non instanziare una RAM per poi caricarci i valori. Definiscili fissi nel tuo codice VHDL, in questo modo dai la possibilità al compiler di fare delle ottimizzazioni.

Usa un case-statement:

- Codice: Seleziona tutto

case Quanto is

when "0000000000" => DbmSignal <= x;

when "0000000001" => DbmSignal <= y;

when others => DbmSignal <= z;

end case;

Questo è un esempio per il caso che il quanto abbia 10 bit.

Puoi togliere l'assegnazione per il caso others se sei sicuro di aver coperto tutti gli altri casi, altrimenti non sintetizzi correttamente!

Adatta i valori assegnati a quello che hai calcolato, compatibilmente con il tipo di DbmSignal.

Per non impestare il codice, metti il tutto in un processo, che infilerai in un'entità (io la chiamerei DbmConverter, o qualcosa del genere). Questa la instanzierai poi nel tuo codice principale come black-box e non dovrai piú curarti di quello che succede al suo interno.

Saluti Boiler

0

voti

ma questo vorrebbe dire però istanziare tutto a mano? cioè finché sono 10 bit ok ma per 16 bit dovrei scrivere 65000 combinazioni?

Io intendevo creare in matlab due array con una semplice formula di conversione e copiarla in memoria

Io intendevo creare in matlab due array con una semplice formula di conversione e copiarla in memoria

0

voti

Da quanto vedo sei molto esperto in materia per cui magari puoi darmi un suggerimento su come inviare i dati da matlab alla scheda, soprattutto come cacciare il livello dei quanti in formato a 10 bit. Poiché di certo matlab utilizzerà un formato suo fissato per elaborazione dati per cui io dovrei in qualche modo forzare i dati in strutture predefinite (registri) a 10 o 16 bit.

11 messaggi

• Pagina 1 di 2 • 1, 2

Chi c’è in linea

Visitano il forum: Nessuno e 12 ospiti

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)