Inverter RTL

Moderatori: ![]() carloc,

carloc, ![]() g.schgor,

g.schgor, ![]() BrunoValente,

BrunoValente, ![]() IsidoroKZ

IsidoroKZ

0

voti

[1] Inverter RTL

Salve, ho un esercizio che mi chiede di progettare un inverter RTL conoscendo la tensione di alimentazione,la capacità da caricare, la VIH e i tempi di salita e di discesa. Per quanto riguarda il tempo di salita lo svolgimento è semplice in quanto il BJT è interdetto e mi troverei a studiare una rete RC, invece, per il tempo di discesa non saprei come impostare lo svolgimento. Potete aiutarmi?

0

voti

[2] Re: Inverter RTL

Devi garantire che la corrente attraverso il transistore sia sufficientemente elevata.

Per usare proficuamente un simulatore, bisogna sapere molta più elettronica di lui

Plug it in - it works better!

Il 555 sta all'elettronica come Arduino all'informatica! (entrambi loro malgrado)

Se volete risposte rispondete a tutte le mie domande

Plug it in - it works better!

Il 555 sta all'elettronica come Arduino all'informatica! (entrambi loro malgrado)

Se volete risposte rispondete a tutte le mie domande

0

voti

[3] Re: Inverter RTL

Nei dati dell'esercizio deve essere indicato il HFE (beta) del transistor.

e imporre una corrente di collettore del transistor quando comandato in ON.

In pratica si può supporre un beta di 30 o 50, il beta di saturazione sempre 30?

E la Vce di saturazione = 0,3 V?

L'uscita dell'inverter è a vuoto o chiusa su un carico ?

Se è un esercizio didattico il progetto è semplice.

A volere fare un vero progetto, la soluzione si complica, non è definita, ci sono diversi gradi di libertà, si dovrebbe supporre un carico costituito da un certo numero di porte NOR uguali pilotate dall'inverter (fanout) e calcolare il margine di funzionamento dei livelli alti e bassi.

e imporre una corrente di collettore del transistor quando comandato in ON.

In pratica si può supporre un beta di 30 o 50, il beta di saturazione sempre 30?

E la Vce di saturazione = 0,3 V?

L'uscita dell'inverter è a vuoto o chiusa su un carico ?

Se è un esercizio didattico il progetto è semplice.

A volere fare un vero progetto, la soluzione si complica, non è definita, ci sono diversi gradi di libertà, si dovrebbe supporre un carico costituito da un certo numero di porte NOR uguali pilotate dall'inverter (fanout) e calcolare il margine di funzionamento dei livelli alti e bassi.

0

voti

[4] Re: Inverter RTL

Sì è un esercizio didattico abbastanza semplice solo che non so come procedere  Tra i dati conosco beta, Vcesat e Vbesat. L'inverter carica una capacità che conosco. Durante la fase di discesa il BJT conduce quindi so che la corrente di scarica è IC e da questa mi ricavo la IB e di conseguenza trovo RB, giusto? ma non so impostare la relazione per ricavarmi la IC. So che mi sfugge una cavolata ma non la trovo

Tra i dati conosco beta, Vcesat e Vbesat. L'inverter carica una capacità che conosco. Durante la fase di discesa il BJT conduce quindi so che la corrente di scarica è IC e da questa mi ricavo la IB e di conseguenza trovo RB, giusto? ma non so impostare la relazione per ricavarmi la IC. So che mi sfugge una cavolata ma non la trovo

0

voti

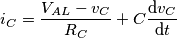

[5] Re: Inverter RTL

La corrente di collettore e` data da quella che arriva dalla resistenza piu` quella che serve per scaricare il condensatore. Quest'ultima rispetta l'equazione differenziale che descrive il comportamento della capacita`.

Da li` in avanti le soluzioni dipendono da come avete impostato il corso e se sai risolvere le eq. diff. oppure se puoi approssimare ad esempio il primo termine (maggiorandolo) ad esempio come VAL/RC

Per usare proficuamente un simulatore, bisogna sapere molta più elettronica di lui

Plug it in - it works better!

Il 555 sta all'elettronica come Arduino all'informatica! (entrambi loro malgrado)

Se volete risposte rispondete a tutte le mie domande

Plug it in - it works better!

Il 555 sta all'elettronica come Arduino all'informatica! (entrambi loro malgrado)

Se volete risposte rispondete a tutte le mie domande

0

voti

[7] Re: Inverter RTL

Aaah okay ho risolto  Posso togliermi un altro dubbio? Quando mi viene chiesto di progettare un buffer CMOS con due inverter in cascata (per quanto riguarda le dimensioni WxL dei due transistor NMOS e PMOS del primo CMOS) devo scegliere entrambe le lunghezze minime L=Lmin? Grazie mille

Posso togliermi un altro dubbio? Quando mi viene chiesto di progettare un buffer CMOS con due inverter in cascata (per quanto riguarda le dimensioni WxL dei due transistor NMOS e PMOS del primo CMOS) devo scegliere entrambe le lunghezze minime L=Lmin? Grazie mille

0

voti

[8] Re: Inverter RTL

Ferz ha scritto:Quando mi viene chiesto di progettare un buffer CMOS con due inverter in cascata (per quanto riguarda le dimensioni WxL dei due transistor NMOS e PMOS del primo CMOS) devo scegliere entrambe le lunghezze minime L=Lmin?

Se è richiesto che il tempo di propagazione del buffer sia minimo, allora sì, visto che la capacità parassita di ingresso del buffer (data dalla somma della capacità di gate dell' n-MOS più la capacità di gate del p-MOS, entrambi relativi al primo inverter) sarà minima in questo caso.

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)