Gli appunti che sto seguendo sono tratti da delle slides di un corso di elettronica digitale basato sul Tocci-Widmer, sullo Spirito ed alcuni datasheet degli integrati reputati più rilevanti.

Attualmente ho a disposizione l'ottava edizione del Tocci e la prima dello Spirito. In prima battuta chiederei se qualcuno ha da suggerirmi qualche buona dispensa riguardo il tema in quanto, se non ho visto male, l'argomento non viene trattato in nessuno dei due testi di cui dispongo.

Teoria

Se non ho capito male, un qualsiasi registro funziona correttamente (nel senso, risponde agli stimoli in modo predicibile secondo la relativa tavola di verità) se i dati in ingresso non variano ''troppo a ridosso'' dei fronti attivi del clock. Per tener conto di questo aspetto si definiscono due tempi caratteristici:

- tempo di setup (

): anticipo minimo con cui il dato in ingresso può cambiare rispetto il prossimo fronte di clock attivo;

): anticipo minimo con cui il dato in ingresso può cambiare rispetto il prossimo fronte di clock attivo; - tempo di hold (

): ritardo minimo con cui il dato in ingresso può cambiare rispetto all'ultimo fronte di clock attivo.

): ritardo minimo con cui il dato in ingresso può cambiare rispetto all'ultimo fronte di clock attivo.

Questi due tempi, congiuntamente al tempo di propagazione dal clock all'uscita (

), comportano un limite superiore alla banda del registro o, in altri termini, alla frequenza massima con cui il clock può variare pur rispettando il corretto funzionamento del registro. Se questi due tempi non vengono rispettati allora il registro, nella peggiore delle ipotesi, può venire a trovarsi in uno stato metastabile, dove la risposta potrebbe non dipendere dagli ingressi.

), comportano un limite superiore alla banda del registro o, in altri termini, alla frequenza massima con cui il clock può variare pur rispettando il corretto funzionamento del registro. Se questi due tempi non vengono rispettati allora il registro, nella peggiore delle ipotesi, può venire a trovarsi in uno stato metastabile, dove la risposta potrebbe non dipendere dagli ingressi.Tipicamente il tempo di hold è di un ordine di grandezza inferiore ai tempi di setup e di propagazione, per cui, senza perdita di generalità, lo si può trascurare.

Un primo semplice esempio

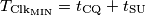

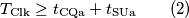

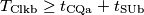

In base a quanto detto segue che la banda di un semplice registro a FFD (flip-flop di tipo D) è data da

Per dimostrare il risultato si ragiona su una possibile temporizzazione, confrontando il periodo di clock con i tempi caratteristici del FFD

Per

intendo il generico valore iniziale dell'uscita, mentre con

intendo il generico valore iniziale dell'uscita, mentre con  intendo la distanza temporale tra la variazione dell'ingresso e il relativo prossimo fronte di clock (la quale deve soddisfare

intendo la distanza temporale tra la variazione dell'ingresso e il relativo prossimo fronte di clock (la quale deve soddisfare  ).

).Dalla temporizzazione si nota facilmente che il periodo di clock

deve essere sufficientemente lungo da permettere all'uscita di commutare e all'ingresso di poter variare con sufficiente anticipo rispetto al relativo prossimo fronte di clock. Questo significa che affinché il registro funzioni correttamente deve essere

deve essere sufficientemente lungo da permettere all'uscita di commutare e all'ingresso di poter variare con sufficiente anticipo rispetto al relativo prossimo fronte di clock. Questo significa che affinché il registro funzioni correttamente deve essere

quindi il periodo minimo si ottiene rispettando al limite (*) la precedente disuguaglianza, ossia

dimostrando così la

.

.(*) nota: la variazione dell'ingresso viene ''sentita'' dal registro se il tempo di setup è rispettato, ossia se cade nell'intervallo che va dal primo fronte di clock a

(alla frequenza massima di lavoro si ha

(alla frequenza massima di lavoro si ha  ).

).Un secondo esempio

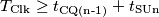

Mi pare ci sia una inconsistenza tra teoria e ''pratica'' quando si va ad analizzare il divisore di frequenza. Anche in questo caso, in base ad un ragionamento analago al precedente, dovrebbe valere la

. Una relativa temporizzazione su cui ragionare è la seguente.

. Una relativa temporizzazione su cui ragionare è la seguente.Il primo problema che mi sto ponendo riguarda il tempo di hold. Se la precedente temporizzazione è corretta, si nota che l'ingresso non è mai stabile immediatamente dopo la commutazione triggerante del clock. Questo significa che, teoricamente, nella pratica non si può realizzare un divisore di frequenza con un FFD in quanto lo schema non può rispettare il tempo di hold a meno che questo non sia nullo.

Tirando le somme, se si trascura

, come si usa fare, nessun problema, ma nella pratica

, come si usa fare, nessun problema, ma nella pratica  per cui la difficoltà è concreta. Nonostante questo, nella pratica si usa realizzare i divisori di frequenza tramite lo schema a FFD.

per cui la difficoltà è concreta. Nonostante questo, nella pratica si usa realizzare i divisori di frequenza tramite lo schema a FFD.Quindi il primo quesito è: dove sta la falla in tutto il discorso che ho fatto?

Ringrazio anticipatamente chiunque abbia voglia di darmi una mano.

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)

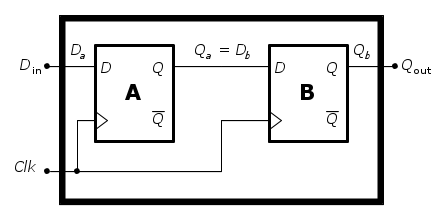

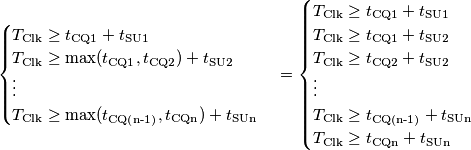

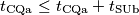

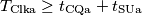

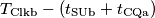

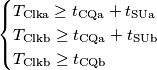

che nel caso

che nel caso  l'ingresso può variare all'interno dell'intervallo proibito

l'ingresso può variare all'interno dell'intervallo proibito  . Se

. Se  , l''unica è che

, l''unica è che

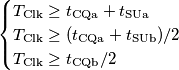

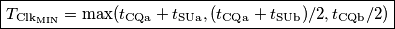

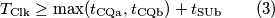

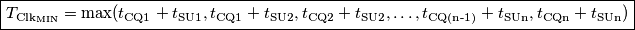

che la

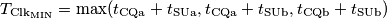

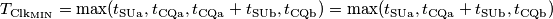

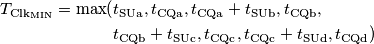

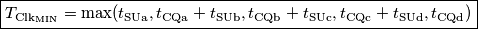

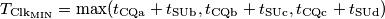

che la  . Il sistema che porta al minimo periodo di clock accettato dal sistema è quindi

. Il sistema che porta al minimo periodo di clock accettato dal sistema è quindi

. Però questo pone già una condizione sul periodo di clock: deve essere almeno

. Però questo pone già una condizione sul periodo di clock: deve essere almeno  .

. ;

; .

. ;

; .

.

.

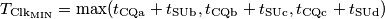

. ;

; .

.

.

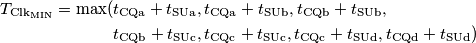

.

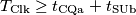

, quindi l'ingresso Db viene sentito se commuta nella finestra di tempo che va da un colpo di clock triggerante e

, quindi l'ingresso Db viene sentito se commuta nella finestra di tempo che va da un colpo di clock triggerante e  .

. ;

; .

.

, pertanto il sistema precedente si riscrive come

, pertanto il sistema precedente si riscrive come