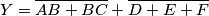

, si chiede di implementare il circuito CMOS statico che realizzi la funzione data. Dopodiché occorre stabilire le combinazioni degli ingressi che producono le commutazioni HL ed LH dell'uscita di caso peggiore, infine occorre dimensionare ciascun transistor affinché i tempi di propagazione LH ed HL siano uguali e che la (W/L)N eq = 2/1 (vedi traccia.jpeg).

, si chiede di implementare il circuito CMOS statico che realizzi la funzione data. Dopodiché occorre stabilire le combinazioni degli ingressi che producono le commutazioni HL ed LH dell'uscita di caso peggiore, infine occorre dimensionare ciascun transistor affinché i tempi di propagazione LH ed HL siano uguali e che la (W/L)N eq = 2/1 (vedi traccia.jpeg).La funzione logica l'ho semplificata come

ed il circuito CMOS è quello nel file rete.jpeg. Considerando la rete PDN, affinché essa sia equivalente ad un transistor con (W/L) = 2/1 ho dimensionato la lunghezza di canale di ciascun NMOS ad 1/5, in modo che 5 NMOS in serie abbiano lunghezza totale pari ad 1. Inoltre gli NMOS in parallelo li ho dimensionati con larghezza unitaria, cosicché il loro parallelo sia equivalente ad un NMOS con W=2. Per concludere, affinché i tempi di commutazione HL ed LH siano gli stessi ho tenuto conto della minor mobilità delle lacune rispetto agli elettroni applicando una (W/L)P eq = 6/1, cioè la larghezza di canale del PMOS equivalente 3 volte superiore a quella di un NMOS.

ed il circuito CMOS è quello nel file rete.jpeg. Considerando la rete PDN, affinché essa sia equivalente ad un transistor con (W/L) = 2/1 ho dimensionato la lunghezza di canale di ciascun NMOS ad 1/5, in modo che 5 NMOS in serie abbiano lunghezza totale pari ad 1. Inoltre gli NMOS in parallelo li ho dimensionati con larghezza unitaria, cosicché il loro parallelo sia equivalente ad un NMOS con W=2. Per concludere, affinché i tempi di commutazione HL ed LH siano gli stessi ho tenuto conto della minor mobilità delle lacune rispetto agli elettroni applicando una (W/L)P eq = 6/1, cioè la larghezza di canale del PMOS equivalente 3 volte superiore a quella di un NMOS. E' corretto questo procedimento? Grazie a tutti!

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)