sbagli perchp non consideri il fattore 1/2 che compare nella formula della corrente di saturazione dei MOS.

EDIT: nel mio post in quella formula ho fatto un typo, ho scritto 1/1 ma è ovviamente 1/2 (il risultato è giusto ed è come se avessi scritto 1/2)

Risoluzione porta logica cmos

Moderatori: ![]() carloc,

carloc, ![]() g.schgor,

g.schgor, ![]() BrunoValente,

BrunoValente, ![]() IsidoroKZ

IsidoroKZ

20 messaggi

• Pagina 2 di 2 • 1, 2

0

voti

Se qualcuno respira per me, volentieri  . Ho ancora una settimana incasinata, poi dovrebbe andare meglio.

. Ho ancora una settimana incasinata, poi dovrebbe andare meglio.

Per usare proficuamente un simulatore, bisogna sapere molta più elettronica di lui

Plug it in - it works better!

Il 555 sta all'elettronica come Arduino all'informatica! (entrambi loro malgrado)

Se volete risposte rispondete a tutte le mie domande

Plug it in - it works better!

Il 555 sta all'elettronica come Arduino all'informatica! (entrambi loro malgrado)

Se volete risposte rispondete a tutte le mie domande

0

voti

La soluzione corredata di simulazione circuitale è già stata proposta, dunque non mi ripeto. Provo piuttosto ad avere un approccio didattico per enfatizzare la metodologia di analisi.

Il problema consiste nel determinare il tempo di carica del nodo di uscita attraverso la serie di tre pMOS.

Quando si ha a che fare con questo tipo di problemi, ci si può sempre ricondurre alla situazione di dover studiare la carica/scarica di un carico tramite un invertitore con dimensionamento equivalente (i.e., un invertitore in cui la dimensione del nMOS e del pMOS è tale per cui la conducibilità dei transistor è equivalente alla conducibilità di una configurazione più complessa di transistori, nel caso specifico la serie di tre pMOS).

Consideriamo dunque il semplice invertitore.

La metodologia per il calcolo del tempo di salita ti è già stata proposta da deltax. Di base si tratta di risolvere un'equazione differenziale eguagliando la corrente nel pMOS alla corrente nella capacità. Durante il primo tratto del transitorio il pMOS è in saturazione (facilmente verificabile) e si ha dunque un transitorio a corrente costante. Successivamente, passa in regione lineare.

deltax. Di base si tratta di risolvere un'equazione differenziale eguagliando la corrente nel pMOS alla corrente nella capacità. Durante il primo tratto del transitorio il pMOS è in saturazione (facilmente verificabile) e si ha dunque un transitorio a corrente costante. Successivamente, passa in regione lineare.

Nel tratto in saturazione, parti da ed arrivi a

ed arrivi a  . Nel tratto in regione lineare parti da

. Nel tratto in regione lineare parti da  ed arrivi a

ed arrivi a  dove con

dove con  si indica la tensione a cui il transitorio di salita si considera esaurito, nello speficico

si indica la tensione a cui il transitorio di salita si considera esaurito, nello speficico

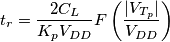

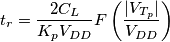

Il tempo di salita complessivo assume una forma del tipo (stiamo ancora parlando dell'invertitore, se qualcosa non ti è chiaro meglio rivedere l'invertitore prima di studiare circuiti CMOS più complessi):

![t_r=\frac{2C_L}{K_p (V_{DD}+V_{T_p})} \left[ \frac{-V_{T_p}}{V_{DD}+V_{T_p}}+\frac{1}{2}\ln{\left[ \frac{2(V_{DD}+V_{T_p})-(V_{DD}-V_{OHmin})}{V_{DD}-V_{OHmin}} \right]} \right] t_r=\frac{2C_L}{K_p (V_{DD}+V_{T_p})} \left[ \frac{-V_{T_p}}{V_{DD}+V_{T_p}}+\frac{1}{2}\ln{\left[ \frac{2(V_{DD}+V_{T_p})-(V_{DD}-V_{OHmin})}{V_{DD}-V_{OHmin}} \right]} \right]](/forum/latexrender/pictures/a037bdff1a4e9f99a16963b4e29592e4.png)

semplificabile come:

dove![F(x)=\frac{1}{1-x}\left[ \frac{x}{1-x} +\frac{1}{2}\ln{\left( 19-20x\right)} \right] F(x)=\frac{1}{1-x}\left[ \frac{x}{1-x} +\frac{1}{2}\ln{\left( 19-20x\right)} \right]](/forum/latexrender/pictures/320742cb603f7a099787c38235efb9bc.png)

E questo è il transitorio 0-90%.

- Cosa comporta considerare come punto di partenza il 10% invece di 0%?

- Cosa comporta considerare la serie di 3 pMOS al posto di un singolo pMOS?

Per concludere:

Non dirmi che hai davvero usato Wolfram per risolvere quell'integrale lì :)

Indizio: sviluppo di Heaviside --> logaritmi

Il problema consiste nel determinare il tempo di carica del nodo di uscita attraverso la serie di tre pMOS.

Quando si ha a che fare con questo tipo di problemi, ci si può sempre ricondurre alla situazione di dover studiare la carica/scarica di un carico tramite un invertitore con dimensionamento equivalente (i.e., un invertitore in cui la dimensione del nMOS e del pMOS è tale per cui la conducibilità dei transistor è equivalente alla conducibilità di una configurazione più complessa di transistori, nel caso specifico la serie di tre pMOS).

Consideriamo dunque il semplice invertitore.

La metodologia per il calcolo del tempo di salita ti è già stata proposta da

Nel tratto in saturazione, parti da

ed arrivi a

ed arrivi a  . Nel tratto in regione lineare parti da

. Nel tratto in regione lineare parti da  ed arrivi a

ed arrivi a  dove con

dove con  si indica la tensione a cui il transitorio di salita si considera esaurito, nello speficico

si indica la tensione a cui il transitorio di salita si considera esaurito, nello speficico

Il tempo di salita complessivo assume una forma del tipo (stiamo ancora parlando dell'invertitore, se qualcosa non ti è chiaro meglio rivedere l'invertitore prima di studiare circuiti CMOS più complessi):

![t_r=\frac{2C_L}{K_p (V_{DD}+V_{T_p})} \left[ \frac{-V_{T_p}}{V_{DD}+V_{T_p}}+\frac{1}{2}\ln{\left[ \frac{2(V_{DD}+V_{T_p})-(V_{DD}-V_{OHmin})}{V_{DD}-V_{OHmin}} \right]} \right] t_r=\frac{2C_L}{K_p (V_{DD}+V_{T_p})} \left[ \frac{-V_{T_p}}{V_{DD}+V_{T_p}}+\frac{1}{2}\ln{\left[ \frac{2(V_{DD}+V_{T_p})-(V_{DD}-V_{OHmin})}{V_{DD}-V_{OHmin}} \right]} \right]](/forum/latexrender/pictures/a037bdff1a4e9f99a16963b4e29592e4.png)

semplificabile come:

dove

![F(x)=\frac{1}{1-x}\left[ \frac{x}{1-x} +\frac{1}{2}\ln{\left( 19-20x\right)} \right] F(x)=\frac{1}{1-x}\left[ \frac{x}{1-x} +\frac{1}{2}\ln{\left( 19-20x\right)} \right]](/forum/latexrender/pictures/320742cb603f7a099787c38235efb9bc.png)

E questo è il transitorio 0-90%.

- Cosa comporta considerare come punto di partenza il 10% invece di 0%?

- Cosa comporta considerare la serie di 3 pMOS al posto di un singolo pMOS?

Per concludere:

deltax ha scritto: bisogna risolvere un integrale un po’ laborioso che io ho risolto con Wolfram Alpha.ps

Non dirmi che hai davvero usato Wolfram per risolvere quell'integrale lì :)

Indizio: sviluppo di Heaviside --> logaritmi

"The past is not really the past until it has been registered. Or put another way, the past has no meaning or existence unless it exists as a record in the present."

John Archibald Wheeler

John Archibald Wheeler

0

voti

DrCox ha scritto:Non dirmi che hai davvero usato Wolfram per risolvere quell'integrale lì :)

Indizio: sviluppo di Heaviside --> logaritmi

Più che altro avrei una domanda (curiosità) per te: secondo te la differenza tra il calcolo esatto e l'approssimazione con Req, che da un errore del 30%, è dovuto a valori troppo alti di Vdd, o questo è un errore "tipico"? A me 30% sembra abbastanza alto come scarto, ma vorrei il parere di qualcuno più esperto.

Riguardo la tua domanda delle conseguenze di condensare 3 pMOS in un singolo pMOS, come dicevo nel post iniziale, si vanno a non considerare i nodi interni, ottenendo quindi situazioni migliorative/peggiorative a seconda della configurazione. Ad esempio in una transizione basso-alto in cui si ha il primo nMOS del pull-down attivo, la rete di pull-up deve caricare sia il nodo di uscita sia il nodo di qel nMOS, risultando in un ritardo addizionale. Questo fenomeno è ignorato quando ci si riporta all'inverter equivalente.

0

voti

deltax ha scritto:Più che altro avrei una domanda (curiosità) per te: secondo te la differenza tra il calcolo esatto e l'approssimazione con Req, che da un errore del 30%, è dovuto a valori troppo alti di Vdd, o questo è un errore "tipico"?

La Req è facile da calcolare in regione lineare. Quanto vale secondo te in saturazione?

deltax ha scritto:in una transizione basso-alto in cui si ha il primo nMOS del pull-down attivo, la rete di pull-up deve caricare sia il nodo di uscita sia il nodo di qel nMOS, risultando in un ritardo addizionale. Questo fenomeno è ignorato quando ci si riporta all'inverter equivalente.

Questo è vero qualora si consideri anche una specifica topologia per il pull-down. Per il problema specifico non è indicata la topologia del PD (non per forza deve essere il duale del Pull-Up), dunque non possiamo fare altro che trascurare eventuali effetti di carico introdotti dal PD stesso.

Trascurando dunque ul pull-down, quali sono i problemi nel considerare il transistor equivalente per il pull-up? Una transizinoe 010 -> 000 è uguale ad una transizione 111 -> 000 per il pull up? Direi che è questa la domanda fondamentale su cui ragionare.

"The past is not really the past until it has been registered. Or put another way, the past has no meaning or existence unless it exists as a record in the present."

John Archibald Wheeler

John Archibald Wheeler

0

voti

DrCox ha scritto:La Req è facile da calcolare in regione lineare. Quanto vale secondo te in saturazione?

la resistenza in saturazione vale zero perché lambda = 0, il MOS si comporta come un generatore di corrente ideale.

Il mio dubbio più che altro era relativo all'errore che si ottiene approssimando con Req e facendo i calcoli giusti. Andando a spulciare ancora un po' nella teoria, ho visto che la formula che ho usato è applicabile per transizioni da Vdd a Vdd/2, per cui non andava bene nel nostro caso.

Tuttavia per curiosità ho provato a fare un calcolo con la corrente media in zona di saturazione, per evitare di risolvere l'integrale.

Ho considerato la corrente iniziale in zona di triodo (per 0.7 V) e quella in zona finale (2.97 V), ho fatto una media della corrente e poi ho applicato la formula della carica di un condensatore. Così si ottiene 758 ps invece di 827 ps. Non so se sia una buona approssimazione...

DrCox ha scritto:Trascurando dunque ul pull-down, quali sono i problemi nel considerare il transistor equivalente per il pull-up? Una transizinoe 010 -> 000 è uguale ad una transizione 111 -> 000 per il pull up? Direi che è questa la domanda fondamentale su cui ragionare.

ci avevo pensato all'inizio. Io penso, ma non sono sicuro, che il PMOS B, essendo già acceso quando il PMOS C commuta 1->0, dovrebbe avere il suo nodo interno già carico, quindi rappresenta una situazione migliorativa rispetto alla commutazione 100 -> 000.

0

voti

deltax ha scritto:ho fatto una media della corrente

E' sempre lecito assumere che l'integrale di una variabile sia equivalente all'integrale del valor medio?

deltax ha scritto:il PMOS B, essendo già acceso quando il PMOS C commuta 1->0, dovrebbe avere il suo nodo interno già carico, quindi rappresenta una situazione migliorativa rispetto alla commutazione 100 -> 000.

Che equivale a considerare la carica come se avvenisse attraverso un transistor equiavlente a quanti transistor di pull-up? 3? 2? altro?

"The past is not really the past until it has been registered. Or put another way, the past has no meaning or existence unless it exists as a record in the present."

John Archibald Wheeler

John Archibald Wheeler

0

voti

DrCox ha scritto:E' sempre lecito assumere che l'integrale di una variabile sia equivalente all'integrale del valor medio?

per me no, ma non so l risposta formale a questa domanda. Quello che volevo (provare a) fare era semplicemente fare un approssimazione per evitare un calcolo laborioso. Essendo un approssimazione è ovvio che non è equivalente, ma non mi aspettavo uno scarto così elevato...

DrCox ha scritto:Che equivale a considerare la carica come se avvenisse attraverso un transistor equiavlente a quanti transistor di pull-up? 3? 2? altro?

così, a occhio, direi "altro"

20 messaggi

• Pagina 2 di 2 • 1, 2

Chi c’è in linea

Visitano il forum: Nessuno e 47 ospiti

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)