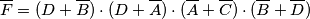

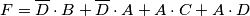

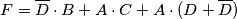

dadothebest ha scritto:

Per quanto rigurada i pass-transistor non so dove mettere mano, ho provato a cercare su internet ma ho trovato solo teoria e gli schemi del NOR e NAND, nient'altro. Non chiedo la pappa pronta ma un qualcosa con cui capire.

disclamair: non ho tempo per fare il circuito, e la soluzione che sto per darti potrebbe essere non ottimizzata.

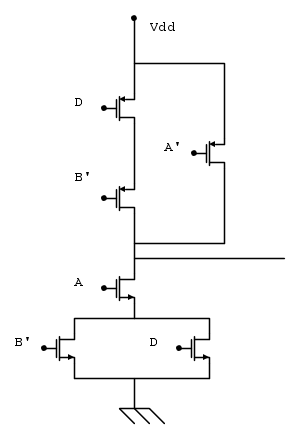

Penso che partendo dalle due implementazioni classiche di AND e OR a pass transistor puoi sviluppare la tua funzione. Ci ho ragionato un po' e non mi smebra sia possibile ottimizzarla circuitalmente senza creare conflitto di nodi (non so se poi si possa semplificare dal punto di vista di pura algebra booleana), ma non è escluso comunque che la soluzione che sto per darti potrebbe avere un numero non minimo di transistor.

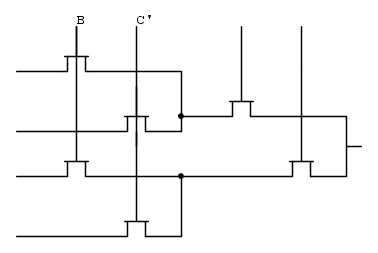

Segui questa immagine:

https://www.google.it/search?q=pass+tra ... 2JJH8wuymM:

Per le due funzioni B*!D e D*!C usa la AND, poi i due output mettili in OR sempre con il circuito in immagine. Noterai che hai bisogno di alcuni input negati per creare i circuiti, quello che puoi fare per ridurre la complessità è scegliere questi input in maniera intelligente in base alla tua funzione logica. In particolare puoi notare che nella funzione compare D e il suo negato, mentre input "singoli" sono A,B e C. Siccome nelle funzioni AND hai bisogno solo di uno dei due input che abbia contemporaneamente il suo valore e quello negato, scegli a questo scopo D, che appunto nella tua funzione compare sia come valore che come suo negato. Quindi avrai due circuiti AND: nel primo, l'ingresso che non necessita del suo negato sarà B, nel secondo !C (in realtà anche uno di questi due deve avere il suo negato, e ora vedrai perché).

Adesso hai la necessità di fare una OR tra gli output dei due AND, chiamiamoli output1 e output2. Sfortunatamente anche in questo caso hai bisogno di almeno uno dei due che abbia anche il suo negato. Quindi uno dei due circuiti AND precedenti deve essere ampliato, come nell'immagine, per dare anche il suo valore negato (4 transistor invece di 2) mentre l'altro può essere lasciato a dare solo la sua funzione senza negarla, con 2 transistor (ma attenzione, in questo caso uno tra B e D avrà bisogno del suo negato! come dicevamo sopra).

Il risultato di output1 OR output2, chiamiamolo output3, sarà messo in OR con !A. Una cosa importante da rimarcare qui è che nelle gate dei transistor devi mettere !A, perché se metti output3, che è già degradato da 2 stage di pass transistor, lo degradi ancora di più: è uno dei fondamentali problemi dei pass transistor, visto che l'nMOS transmette un 1 debole, e il problema deve essere minimizzato il più possibile evitando di collegare le uscite di un pass transistor al gate dello stage successivo del pass transistor.

Nel caso del nostro esempio, avrai due voltage drop. Assumendo il livello alto dei segnali Vdd e la tensione di soglia dei transistor Vt, nei primi 2 stage (AND) avrai output1 e output2 che avranno valori alti di Vdd-Vt. Output 3 avrà valore alto di Vdd-2Vt. Infine l'output finale, F, avrà valore alto Vdd-2Vt SOLO se metti !A come ingresso al gate dell'ultimo stage, facendo il contrario avresti valore alto di F pari a Vdd-3Vt.

A margine dell'esercizio, per risolvere i problemi sopracitati ci sono 2 modi: o usi level restorer, che caricano i nodi ai valori nominali quando alti; o usi la logica a transmission gate, dove al nMOS viene messo un parallelo di pMOS che permette di trasferire entrambi i valori logici forti. Ovviamente entrambe le soluzioni fanno aumentare il numero di transistor.

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)