Salve ragazzi, innanzitutto complimenti a tutti per il forum, mi è stato di aiuto molte volte in passato.

Volevo domandarvi qualche delucidazione sul concetto di clock skew, in particolare quali solo le relazioni matematiche che devono essere rispettate per il corretto funzionamento del circuito. Lo domando perché il mio docente nell'ultimo appello ha inserito una richiesta, "verificare se il circuito funziona oppure se ci sono problemi causati da clock skew". Ora, poiché durante il corso, tenuto da un altro docente, di clock skew non se ne è sentito mai neanche l'eco, tutti abbiamo saltato quella richiesta non sapendo quanto valesse effettivamente a livello di punteggio. Cercando in internet ho più o meno capito che si tratta di un problema dovuto al ritardo di propagazione del clock quando è condiviso tra diversi flip flops. In poche parole il clock non arriva contemporaneamente ad entrambi i flip flop e questo causa problemi alla corretta acquisizione dei dati.

Potreste per favore aiutarmi a tradurre questa cosa in relazioni matematiche, tenendo conto di entrambe le possibili direzioni della propagazione dei dati? Grazie mille, so che probabilmente la domanda è scema, ma non riesco proprio a capire.

Clock Skew

Moderatori: ![]() carloc,

carloc, ![]() g.schgor,

g.schgor, ![]() BrunoValente,

BrunoValente, ![]() IsidoroKZ

IsidoroKZ

5 messaggi

• Pagina 1 di 1

3

voti

[2] Re: Clock Skew

Il clock skew è la differenza tra l'istante atteso di clock e il clock effettivo ed è un problema presente tipicamente quando il segnale di clock deve comandare molti elementi (vedendo quindi un'elevata capacità).

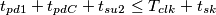

In sede di analisi il clock skew deve essere considerato nella situazione di caso pessimo, per verificare se anche in questo caso non sono violati i vincoli imposti dalla disciplina dinamica. In pratica puoi vedere la cosa come se il nuovo tempo di setup del flip flop diventasse e il tempo di hold

e il tempo di hold

In sede di analisi il clock skew deve essere considerato nella situazione di caso pessimo, per verificare se anche in questo caso non sono violati i vincoli imposti dalla disciplina dinamica. In pratica puoi vedere la cosa come se il nuovo tempo di setup del flip flop diventasse

e il tempo di hold

e il tempo di hold

Electronic devices operate because they contain magic smoke. If the magic smoke is ever let out of the device, it ceases to work.

1

voti

[3] Re: Clock Skew

Grazie mille per la risposta.

Ok quindi è come se il tempo di clock dovesse aspettare un ulteriore Tskew per fare si che il circuito funzioni. Ok, e nel caso di propagazione dei dati in verso opposto?

Mi spiego:

Fai conto ho due flip flop e in mezzo una rete combinatoria. Il clock arriva in ritardo sul flip flop più lontano, poniamo quello a destra della rete. Se fosse che adesso il dato si propaga da destra verso sinistra, cos'è che cambia nelle condizioni del clock? E' questa parte che non capisco, quando la propagazione è in verso opposto.

Ok quindi è come se il tempo di clock dovesse aspettare un ulteriore Tskew per fare si che il circuito funzioni. Ok, e nel caso di propagazione dei dati in verso opposto?

Mi spiego:

Fai conto ho due flip flop e in mezzo una rete combinatoria. Il clock arriva in ritardo sul flip flop più lontano, poniamo quello a destra della rete. Se fosse che adesso il dato si propaga da destra verso sinistra, cos'è che cambia nelle condizioni del clock? E' questa parte che non capisco, quando la propagazione è in verso opposto.

-

Teslacoil1992

Teslacoil1992

5 2 - Messaggi: 2

- Iscritto il: 17 gen 2014, 15:00

4

voti

[4] Re: Clock Skew

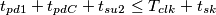

Non si ragiona per vicino o lontanto, la progettazione robusta richiede di considerare in ogni caso il worst case. Non è detto che il clock skew sia lo stesso ad ogni ciclo può essere sia in ritardo che in anticipo ed è per questo che ti metti sempre nella situazione più sfavorevole. Quando valuti i requisiti del tempo di setup immagini che il clock sia anticipato, quando valuti se è soddisfatto il tempo di hold che sia in ritardo, questo a prescindere dalla posizione del flip flop.

Electronic devices operate because they contain magic smoke. If the magic smoke is ever let out of the device, it ceases to work.

4

voti

[5] Re: Clock Skew

Cominciamo da Adamo ed Eva.

Lo skew è la differenza nel tempo d'arrivo dello stesso fianco attivo del clock in due punti diversi dello stesso dominio di clock.

La differenza nel tempo d'arrivo di due fianchi conecutivi allo stesso punto nello stesso dominio si chiama invece jitter.

La causa principale dello skew è il clock distribution delay, ovvero il tempo che deve percorrere il segnale di clock dalla sua sorgente attraverso l'albero di distribuzione fino alla sua destinazione.

Le formule che definiscono le condizioni da soddisfare dipendono dal tipo di clocking usato. Dato che non lo definisci, suppongo tu utilizzi il classico schema a singolo fianco attivo monofase.

Abbiamo il flipflop 1, la cui uscita entra in una logica combinatoria C che va poi ad un flipflop 2.

Definiamo quanto segue:

il ritardo dalla sorgente del clock al FF *

il ritardo dalla sorgente del clock al FF *

il propagation delay

il propagation delay

il periodo del clock

il periodo del clock

il setup time

il setup time

lo skew

lo skew

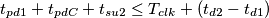

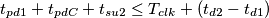

Condizione di setup:

Come puoi vedere, se i ritardi introdotti dalla distribuzione sono uguali, non c'è skew e la formula si riduce a quella nota. Se c'è skew, e se il clock arriva prima a 1 (trasmettitore) e dopo a 2 (ricevitore), allora è positivo. Lo skew positivo aumenta il tempo a disposizione della logica combinatoria per raggiungere uno stato stabile, è quindi utile.

Se i dati vanno da destra verso sinistra (e qui rispondiamo alla tua seconda domanda) allora il trasmettitore diventa ricevitore e viceversa. Lo skew positivo diventa quindi negativo e sottrae tempo alla logica combinatoria. Il margine di setup si riduce, non è una buona cosa.

È tardi... ti lascio calcolare da solo l'effetto sulla condizione di hold. Perlomeno provaci. Se non ci riesci, racconta dove hai incontrato difficoltà.

Ciao Boiler

Lo skew è la differenza nel tempo d'arrivo dello stesso fianco attivo del clock in due punti diversi dello stesso dominio di clock.

La differenza nel tempo d'arrivo di due fianchi conecutivi allo stesso punto nello stesso dominio si chiama invece jitter.

La causa principale dello skew è il clock distribution delay, ovvero il tempo che deve percorrere il segnale di clock dalla sua sorgente attraverso l'albero di distribuzione fino alla sua destinazione.

Le formule che definiscono le condizioni da soddisfare dipendono dal tipo di clocking usato. Dato che non lo definisci, suppongo tu utilizzi il classico schema a singolo fianco attivo monofase.

Abbiamo il flipflop 1, la cui uscita entra in una logica combinatoria C che va poi ad un flipflop 2.

Definiamo quanto segue:

il ritardo dalla sorgente del clock al FF *

il ritardo dalla sorgente del clock al FF * il propagation delay

il propagation delay il periodo del clock

il periodo del clock il setup time

il setup time lo skew

lo skewCondizione di setup:

Come puoi vedere, se i ritardi introdotti dalla distribuzione sono uguali, non c'è skew e la formula si riduce a quella nota. Se c'è skew, e se il clock arriva prima a 1 (trasmettitore) e dopo a 2 (ricevitore), allora è positivo. Lo skew positivo aumenta il tempo a disposizione della logica combinatoria per raggiungere uno stato stabile, è quindi utile.

Se i dati vanno da destra verso sinistra (e qui rispondiamo alla tua seconda domanda) allora il trasmettitore diventa ricevitore e viceversa. Lo skew positivo diventa quindi negativo e sottrae tempo alla logica combinatoria. Il margine di setup si riduce, non è una buona cosa.

È tardi... ti lascio calcolare da solo l'effetto sulla condizione di hold. Perlomeno provaci. Se non ci riesci, racconta dove hai incontrato difficoltà.

Ciao Boiler

5 messaggi

• Pagina 1 di 1

Chi c’è in linea

Visitano il forum: Nessuno e 70 ospiti

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)