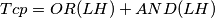

Il circuito è questo:

So che per la frequenza max è l'inverso del periodo minimo.

Il periodo deve essere maggiore del tempo di ritardo del flip flop all'ingresso, del tempo di ritardo della rete combinatoria (critical path) e del tempo di setup del flip flop di uscita. Giusto?

Ora ho alcuni dubbi:

- per il flip flop e per gli elementi del circuito combinatorio, va considerato il tempo di ritardo alto-basso o quello basso-alto?

- per calcolare i tempi di ritardo di ogni porta devo tenere in considerazione il carico (la somma dei load factor delle porte collegate all'uscita), giusto?

come tratto il feedback che c'è tra l'uscita del flip-flop_out e la porta OR?

- all'ingresso ho due flip flop. Quale va preso in considerazione?

Considero i due percorsi flip-flop_in_1 -> OR -> AND -> flip-flop_out e flip-flop_in_2 -> AND -> flip-flop_out e poi prendo il periodo del percorso più lento?

- se ho molte porte può volerci molto tempo. C'è la possibilità di scartare a priori alcuni percorsi?

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)