dovrei dimensionare il rapporto W del seguente PMOS.

Ho già la soluzione, ma sinceramente non l'ho compresa.

Ecco il circuito:

con

e

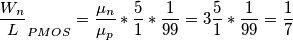

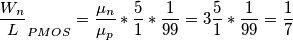

la soluzione è

ma da dove sbuca quel 1/99? cosa è?

Moderatori: ![]() carloc,

carloc, ![]() g.schgor,

g.schgor, ![]() BrunoValente,

BrunoValente, ![]() IsidoroKZ

IsidoroKZ

Data la funzione Y = (A' + B' + C') * (D' + E') * (B + D) disegnare lo schema circuitale del circuito TTL , pseudo NMOS e CMOS che realizza la funzione data. Relativamente ai circuiti pseudo NMOS e CMOS stabilire le combinazioni degli ingressi che producono le commutazione HL e LH dell’uscita di caso peggiore e spiegare perché. Quindi dimensionare tutti i transistor del circuito NMOS e CMOS in modo da ottenere nei casi peggiori tpLH = tpHL (CMOS) e (W/L)N EQU.= 5/1 (unità di Lmin) sapendo che µn/µp = 3.

Bernheart ha scritto:Beh è 0V l'uscita bassa di solito, no?

Io non so che pesci prendere, tu come arriveresti a calcolare quel 1/99?

per i Pmos devi tenere conto che

per i Pmos devi tenere conto che

Visitano il forum: Nessuno e 56 ospiti