da

da  nordest » 23 dic 2019, 12:09

nordest » 23 dic 2019, 12:09

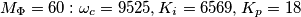

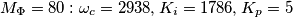

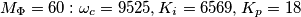

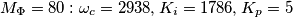

Buongiorno. Vi chiedo per favore di provare a capire che problema potrebbe esserci dietro a come ho progettato il controllo. Teoricamente il modello simulink dovrebbe dare complessivamente la stessa FDT che io trovo teoricamente. Ci sono due anelli, quello interno per la corrente (coordinate d/q) e quello esterno per la velocità. Io ho fatto il controllore PI in entrambi i casi e vedo che imponendo un margine di fase di 60° risulta che per l'anello di corrente da pulsazioni di attraversamento giustamente a frequenza più alta che per 80° ma è instabile. Penso sia dovuto alle discretizzazioni interne che cambiano l'andamento della fase in alta frequenza alternando quindi anche la fase per la pulsazione di attraversamento

. Infatti con un margine di fase di 80° ho una buona stabilità, guadagni più bassi ma anche pulsazioni di attraversamento più basse. Qui vi mostro come ho fatto i conti:

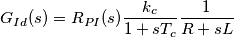

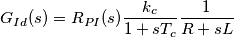

Per l'anello di

(perché più critico di

),

Dove

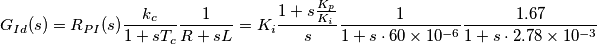

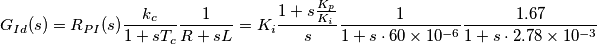

=1 guadagno inverter, R=0.6Ohm resistenza statore,L=1.67mH induttanza, Tc=60us costante di tempo dovuta allo switching dell'inverter.

Voglio con il regolatore semplificare il primo polo dovuto a R,L e impongo le condizioni di margine di fase etc e trovo:

Per l'anello esterno che controlla la velocità ho solo fatto un PI con margine di fase 80 ma non vado avanti a rendere il post troppo lungo, ve ne parlo più avanti se volete ma tanto il problema si vede qui nell'anello interno.

. Infatti con un margine di fase di 80° ho una buona stabilità, guadagni più bassi ma anche pulsazioni di attraversamento più basse. Qui vi mostro come ho fatto i conti:

. Infatti con un margine di fase di 80° ho una buona stabilità, guadagni più bassi ma anche pulsazioni di attraversamento più basse. Qui vi mostro come ho fatto i conti: (perché più critico di

(perché più critico di  ),

),

=1 guadagno inverter, R=0.6Ohm resistenza statore,L=1.67mH induttanza, Tc=60us costante di tempo dovuta allo switching dell'inverter.

=1 guadagno inverter, R=0.6Ohm resistenza statore,L=1.67mH induttanza, Tc=60us costante di tempo dovuta allo switching dell'inverter.

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)