già...ireon ha scritto:Si in effetti viene negativa comunque....

Eh allora dato che non ci può essere una corrente che esce dalla base di un NPN (almeno che non si arrivi al breakdown ma lasciamo perdere...) vuol dire che "L'ipotesi fatta di saturazione è sbagliata" come del resto già anticipato in [2] e [6].

Io direi che è in ZAD

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)

. Comunque il circuito completo dell'esercizio è il seguente:

. Comunque il circuito completo dell'esercizio è il seguente:

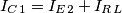

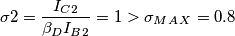

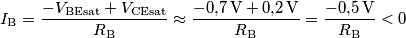

e [unparseable or potentially dangerous latex formula]

e [unparseable or potentially dangerous latex formula] sarà maggiore di

sarà maggiore di  quando [unparseable or potentially dangerous latex formula]

quando [unparseable or potentially dangerous latex formula]

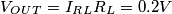

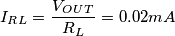

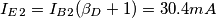

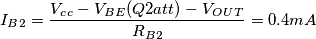

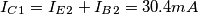

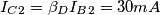

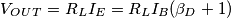

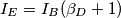

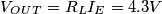

supponendo che il transistor di sopra lavori in regione attiva diretta, naturalmente il transistor sotto è interdetto in questa situazione. Quindi:

supponendo che il transistor di sopra lavori in regione attiva diretta, naturalmente il transistor sotto è interdetto in questa situazione. Quindi:

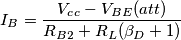

![I_B=\frac{[V_c_c-V_B_E (att)+V_O_U_T]}{R_B_2} I_B=\frac{[V_c_c-V_B_E (att)+V_O_U_T]}{R_B_2}](/forum/latexrender/pictures/f90f14075e789513f479c2d73c7bc2c3.png)

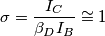

e il transistor sopra

e il transistor sopra  . Supponiamo il transistor

. Supponiamo il transistor