Nei datasheet di IC (circuiti integrati) si legge spesso ad esempio "tempo di propagazione tipico con 50pF di carico: ... ns", volevo capire meglio proprio questo valore di carico capacitivo.

Senza resistenze inoltre il tempo di carica del condensatore dovrebbe essere istantaneo (ovviamente una piccola resistenza in realtà c'è sempre), nei datasheet avrebbero quindi dovuto specificare anche la resistenza e non solo la capacità...

Non riesco inoltre a capire inoltre come la frequenza e la capacità abbassino il livello (la tensione) del segnale: l'impedenza dei condensatori è Z= 1/j*2*pi*f*C, all'aumentare della frequenza e della capacità dovrebbe quindi ridursi la "resistenza"...

Se collego con un filo molto corto (5 cm) il pin dell'IC ad un altro IC o ad un pin header

che carico capacitivo posso avere? Esiste una formula empirica o bisogna comprare un qualche strumento? Che caratteristiche deve avere per fare misure di questo genere?

Ciao e grazie a tutti

Capacità di carico

Moderatori: ![]() carloc,

carloc, ![]() g.schgor,

g.schgor, ![]() BrunoValente,

BrunoValente, ![]() IsidoroKZ

IsidoroKZ

4 messaggi

• Pagina 1 di 1

0

voti

tazzo ha scritto:nei datasheet avrebbero quindi dovuto specificare anche la resistenza e non solo la capacità...

Non è così semplice: l'uscita di una porta logica in commutazione non può essere modellata come una semplice resistenza.

tazzo ha scritto:Se collego con un filo molto corto (5 cm) il pin dell'IC ad un altro IC o ad un pin header

che carico capacitivo posso avere?

Al più pochi pF, ma quei 50 pF possono rappresentare l'effetto di più ingressi di integrati successivi connessi alla stessa uscita.

It's a sin to write  instead of

instead of  (Anonimo).

(Anonimo).

...'cos you know that ain't

ain't  , right?

, right?

You won't get a sexy tan if you write in lieu of

in lieu of  .

.

Take a log for a fireplace, but don't take for

for  arithm.

arithm.

instead of

instead of  (Anonimo).

(Anonimo)....'cos you know that

ain't

ain't  , right?

, right?You won't get a sexy tan if you write

in lieu of

in lieu of  .

.Take a log for a fireplace, but don't take

for

for  arithm.

arithm.-

DirtyDeeds

DirtyDeeds

55,9k 7 11 13 - G.Master EY

- Messaggi: 7012

- Iscritto il: 13 apr 2010, 16:13

- Località: Somewhere in nowhere

2

voti

Elettro-tecnicamente è in realtà un modello corretto. Considera un generico stadio di output di un microcontrollore, di un comparatore di tensione o di un integrato con un uscita digitale: otterrai (ovviamente) un circuito con componenti che nella transizione impiegano un certo periodo per accendersi, ad esempio uno stadio CMOS o uno open collector:

La capacità si carica e si scarica attraverso giunzioni e canali che attraversano varie regioni (saturazione e triodo, interdizione, ecc ecc).

Per semplificarti le idee puoi immaginare che in ogni momento il componente sia una resistenza che si interpone non linearmente tra le alimentazioni e la capacità di test esterna (o le capacità parassite di componenti a valle).

La scarica di una capacità caricata a Vdd attraverso l'NMOS del primo stadio incontra una situazione di saturazione e di triodo, fino a scaricarsi completamente per dare una tensione drain/source nulla sul transistor.

L'ideale sarebbe un tempo di propagazione molto basso. Il problema ovvio è che per ottenerlo la "resistenza" offerta dagli stadi di uscita deve essere molto bassa, e una cosa di questo genere la si ottiene aumentando i dimensionamenti dei MOS o le aree di giunzione degli NPN (la resistenza di pullup è un'altra storia), quindi l'integrato non sarebbe più molto integrato ma sarebbe molto più grande.

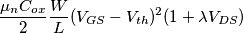

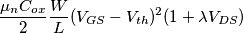

La corrente di drain per un MOSFET in saturazione è

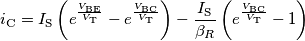

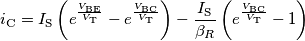

e quella di collettore per un BJT npn acceso

L'area di giunzione del BJT definisce la corrente di polarizzazione inversa venendo moltiplicata per il vettore densità di corrente:

mentre il dimensionamento del MOS è

La capacità si carica e si scarica attraverso giunzioni e canali che attraversano varie regioni (saturazione e triodo, interdizione, ecc ecc).

Per semplificarti le idee puoi immaginare che in ogni momento il componente sia una resistenza che si interpone non linearmente tra le alimentazioni e la capacità di test esterna (o le capacità parassite di componenti a valle).

La scarica di una capacità caricata a Vdd attraverso l'NMOS del primo stadio incontra una situazione di saturazione e di triodo, fino a scaricarsi completamente per dare una tensione drain/source nulla sul transistor.

L'ideale sarebbe un tempo di propagazione molto basso. Il problema ovvio è che per ottenerlo la "resistenza" offerta dagli stadi di uscita deve essere molto bassa, e una cosa di questo genere la si ottiene aumentando i dimensionamenti dei MOS o le aree di giunzione degli NPN (la resistenza di pullup è un'altra storia), quindi l'integrato non sarebbe più molto integrato ma sarebbe molto più grande.

La corrente di drain per un MOSFET in saturazione è

e quella di collettore per un BJT npn acceso

L'area di giunzione del BJT definisce la corrente di polarizzazione inversa venendo moltiplicata per il vettore densità di corrente:

mentre il dimensionamento del MOS è

-

marioursino

marioursino

5.687 3 9 13 - G.Master EY

- Messaggi: 1598

- Iscritto il: 5 dic 2009, 4:32

4 messaggi

• Pagina 1 di 1

Chi c’è in linea

Visitano il forum: Nessuno e 48 ospiti

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)