resistenza pull-up

Moderatori: ![]() carloc,

carloc, ![]() g.schgor,

g.schgor, ![]() BrunoValente,

BrunoValente, ![]() IsidoroKZ

IsidoroKZ

13 messaggi

• Pagina 1 di 2 • 1, 2

0

voti

Ciao a tutti una domanda stupida:

come si calcola la resistenza di pull-up da mettere sul pin di uscita di un opto-isolatore open-collector?

Il pin di uscita andrebbe a finire in un i/o di una fpga

come si calcola la resistenza di pull-up da mettere sul pin di uscita di un opto-isolatore open-collector?

Il pin di uscita andrebbe a finire in un i/o di una fpga

0

voti

Se il circuito è questo:

EDIT: E non è una resistenza di pull - up!

Questa è una resistenza di pull - up

EDIT: E non è una resistenza di pull - up!

Questa è una resistenza di pull - up

0

voti

Ci sono diversi modi per calcolare la resistenza di collettore (o di emettitore, vedila come vuoi) di un opto.

Dipende da diversi fattori e da cosa vuoi ottenere.

Dovresti spiegare l' applicazione in modo dettagliato.

Hai accennato ad una FPGA il che vuol dire tutto e niente.

Dipende da diversi fattori e da cosa vuoi ottenere.

Dovresti spiegare l' applicazione in modo dettagliato.

Hai accennato ad una FPGA il che vuol dire tutto e niente.

"La follia sta nel fare sempre la stessa cosa aspettandosi risultati diversi".

"Parla soltanto quando sei sicuro che quello che dirai è più bello del silenzio".

Rispondere è cortesia, ma lasciare l'ultima parola ai cretini è arte.

"Parla soltanto quando sei sicuro che quello che dirai è più bello del silenzio".

Rispondere è cortesia, ma lasciare l'ultima parola ai cretini è arte.

-

TardoFreak

TardoFreak

73,9k 8 12 13 - -EY Legend-

- Messaggi: 15754

- Iscritto il: 16 dic 2009, 11:10

- Località: Torino - 3° pianeta del Sistema Solare

0

voti

TardoFreak ha scritto:Ci sono diversi modi per calcolare la resistenza di collettore (o di emettitore, vedila come vuoi) di un opto.

Dipende da diversi fattori e da cosa vuoi ottenere.

Dovresti spiegare l' applicazione in modo dettagliato.

L'opto separa la sezione della scheda che tramite una fpga genera un'oda quadra (frequenza tra i 5 e 15 kHz) che sarà ricevuta da un'altra fpga sull'altra sezione.

0

voti

Ecco, i 15 kHz possono essere un problema per molti optoisolatori.

Ora devi dire tutto:

- Sigla dell' optoisolatore che intendi utilizzare.

- Link al datasheet

- Tutte le informazioni riguardanti il segnale da isolare

- Altre ed eventuali.

Ora devi dire tutto:

- Sigla dell' optoisolatore che intendi utilizzare.

- Link al datasheet

- Tutte le informazioni riguardanti il segnale da isolare

- Altre ed eventuali.

"La follia sta nel fare sempre la stessa cosa aspettandosi risultati diversi".

"Parla soltanto quando sei sicuro che quello che dirai è più bello del silenzio".

Rispondere è cortesia, ma lasciare l'ultima parola ai cretini è arte.

"Parla soltanto quando sei sicuro che quello che dirai è più bello del silenzio".

Rispondere è cortesia, ma lasciare l'ultima parola ai cretini è arte.

-

TardoFreak

TardoFreak

73,9k 8 12 13 - -EY Legend-

- Messaggi: 15754

- Iscritto il: 16 dic 2009, 11:10

- Località: Torino - 3° pianeta del Sistema Solare

0

voti

TardoFreak ha scritto:Ecco, i 15 kHz possono essere un problema per molti optoisolatori.

Ora devi dire tutto:

- Sigla dell' optoisolatore che intendi utilizzare.

- Link al datasheet

- Tutte le informazioni riguardanti il segnale da isolare

- Altre ed eventuali.

http://www.datasheetcatalog.org/datashe ... NW2611.pdf

onda quadra frequenza già detta 0-5Volt e poi non so che altro aggiungere

0

voti

A Pag. 15 e 16 trovi il circuito con i grafici. Nei grafici sono riportati i valori dei componenti e dai grafici riesci a determinarti i valori che meglio si adattano alla tua applicazione.

"La follia sta nel fare sempre la stessa cosa aspettandosi risultati diversi".

"Parla soltanto quando sei sicuro che quello che dirai è più bello del silenzio".

Rispondere è cortesia, ma lasciare l'ultima parola ai cretini è arte.

"Parla soltanto quando sei sicuro che quello che dirai è più bello del silenzio".

Rispondere è cortesia, ma lasciare l'ultima parola ai cretini è arte.

-

TardoFreak

TardoFreak

73,9k 8 12 13 - -EY Legend-

- Messaggi: 15754

- Iscritto il: 16 dic 2009, 11:10

- Località: Torino - 3° pianeta del Sistema Solare

5

voti

gohan ha scritto:EDIT: E non è una resistenza di pull - up!

Perche' dici che non e` una resistenza di pull-up? a me sembra che lo sia!

Per fare questi conti e` necessario cononscere le caratteristiche della porta OC (o delle porte OC se ce ne sono piu` di una collegate insieme) e di tutti i carichi che vengono collegati all'uscita OC. In questo caso il carico e` l'ingresso di una FPGA che vuol dire corrente statica assorbita/erogata praticamente nulla e dal punto di vista dinamico un carico capacitivo.

L'idea base e` questa: si verificano separatamente che sia il livello basso che quello alto siano generati correttamente e si trova un intervallo di possibili resistenze di pull-up.

Quando si analizza il livello alto si trova un limite massimo alla Rpu. Se si alza ancora la resistenza oltre questo valore non si ha piu` il livello alto. Per il livello alto bisogna decidere una tensione di livello alto VH, ad esempio potrebbero essere 3V, o ache di piu`, 4V se l'ingresso della FPGA non e` ttl compatibile e ha la soglia a 2.5V circa.

Poi bisogna conoscere la tensione minima di alimentazione Vmin, la corrente assorbita da tutti i carichi collegati all'OC a livello alto, cioe` le loro IIH, e la corrente IOH della porta OC. Quest'ultimo dato e` importante e dice che quando la porta OC dovrebbe idealmente essere un circuito aperto, in realta` assorbe ancora un po' di corrente. Il dato IOH nel caso di OC e` un valore positivo (corrente entrante).

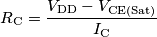

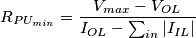

Il circuito di riferimento per il livello alto e` questo

e si vuole scegliere la resistenza di pull-up per garantire il valore di VH minimo che si e` scelto. La resistenza la si calcola con la legge di Ohm, in essa scorre la corrente data dalla somma di tutte le IOH delle porte OC collegate al nodo piu` la somma di tutte le IIH dei carichi collegati

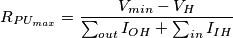

Nel tuo caso c'e` un solo OC che pilota, con una IOH=100uA (data sheet pagina 10, primo parametro: leggere sempre gli asterischi e le note). La corrente di ingresso dei carichi e` nulla, la tensione minima di alimentazione puo` essere ad esempio di 4.75V, la tensione VH che vogliamo garantire e` di 4V e quindi si ha

Il calcolo a livello basso lo si fa in queste condizioni: si assume che la tensione di alimentazione sia al valore massimo, che sull'uscita OC ci sia la tensione VOL definita dalla porta OC e che tutti i carichi riversino verso la porta la loro corrente IIL. In questo caso bisogna scegliere la resistenza di pull-up abbastanza grande da non superare con la corrente totale il valore di IOL della porta che sta attivando il livello basso. Anche se ce ne sono piu` in parallelo, si considera che solo una porta stia assorbendo corrente.

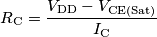

Il circuito di riferimento per questo calcolo e` il seguente:

Si vuole scegliere il valore della resistenza di pull-up in modo che, malgrado tutto, la corrente di ingresso nella porta che pilota il livello basso sia minore o uguale alla IOL.

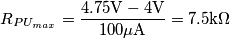

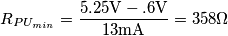

La corrente che puo` passare nella resistenza di pull-up e` quindi dato dalla IOL della porta meno la somma di tutte le correnti che arrivano dai carichi. Da notare che in generale le correnti IIL sono negative perche' uscenti dagli ingressi. Per non fare pasticci con i segni meno, di solito metto dei moduli. Il valore minimo della resistenza vale quindi

In questo caso la VOL vale 0.6V (data sheet pagina 10 terzo parametro), la Vmax la prendiamo 5% al di sopra della alimentazione nominale, quindi sara` 5.25V, la IOL e` di 13mA, ed e` specificata nella stessa riga della VOL, nella colonna delle test conditions. Anche qui il carico statico e` nullo e quindi si ha

In questo intervallo di valori va tutto bene, se non fosse per un dettaglio. I conti fatti sono abbastanza INUTILI perche' nel data sheet, pagina 9 ultimo parametro c'e` scritto l'intervallo raccomandato della resistenza di pull-up, da 330ohm a 4kohm. Pero` fare i calcoli serve per rendersi conto da dove arrivano i valori indicati.

Scegliere una resistenza di pull-up piu` verso l'estremo basso oppure quello alto dell'intervallo trovato ha delle conseguenze sul comportamento del circuito.

Una resistenza di pull-up bassa aumenta il consumo di corrente, ma rende i fronti di salita piu` ripidi, quindi minore ritardo e minore tempo di salita. Il contrario si ha se si sceglie una resistenza di pull-up vicino al valore massimo: circuito energeticamente risparmioso ma lento.

Avendo gia` sbrodolato a lungo taglio qui, senza andare a discutere in dettaglio gli aspetti dinamici.

Per usare proficuamente un simulatore, bisogna sapere molta più elettronica di lui

Plug it in - it works better!

Il 555 sta all'elettronica come Arduino all'informatica! (entrambi loro malgrado)

Se volete risposte rispondete a tutte le mie domande

Plug it in - it works better!

Il 555 sta all'elettronica come Arduino all'informatica! (entrambi loro malgrado)

Se volete risposte rispondete a tutte le mie domande

13 messaggi

• Pagina 1 di 2 • 1, 2

Chi c’è in linea

Visitano il forum: Google Adsense [Bot] e 71 ospiti

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)