Esercizio sui transistor

Moderatori: ![]() carloc,

carloc, ![]() g.schgor,

g.schgor, ![]() BrunoValente,

BrunoValente, ![]() IsidoroKZ

IsidoroKZ

16 messaggi

• Pagina 2 di 2 • 1, 2

5

voti

1

voti

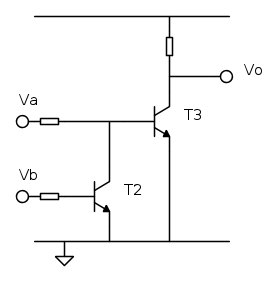

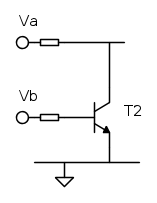

Sia T2 che T3 sono in utilizzati come inverter di segnale. Il potenziale sul collettore, la generica uscita, è invertito rispetto al potenziale di base. Trascurando i valori assoluti delle tensioni, (perché ha poco senso nei circuiti logici), ma assegnando al potenziale V+ un generico significato "1", ed al potenziale 0V un generico significato "0", allora si vede chiaramente che sia T2 che T3 sono due inverter.

Infatti, per il livello logico 0 in base, (transistor interdetto), la tensione di collettore sarà al massimo, quindi livello logico 1. Per un livello logico 1 in base, ovvero tensione alta e transistor in conduzione, il potenziale di collettore sarà praticamente nullo, cioè livello logico 0.

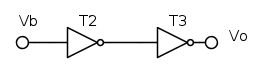

Come primo passaggio quindi possiamo dire che T2 e T3 sono degli inverter:

In prima apparenza, T3 e T2 sembrano essere in cascata tra di loro:

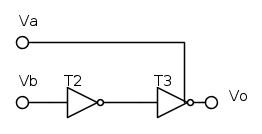

In verità non è così. All'appello, nell'ultimo schema, manca ancora l'ingresso Va.

Va è collegato in modo particolare. Il transistor T3 può condurre solo se Va è a livello logico alto. Se Va è a livello logico basso, T3 sarà certamente interdetto, con 0 i base ed 1 in uscita, indipendentemente dallo stato di T3. Una sorta di Enable.

Quest'ultimo è quindi lo schema logico di quanto realizza il circuito.

-

Candy

Candy

32,5k 7 10 13 - CRU - Account cancellato su Richiesta utente

- Messaggi: 10123

- Iscritto il: 14 giu 2010, 22:54

-1

voti

Candy ha scritto:

Che porta è T3? Non ne ho mai viste disegnate così. Potrebbe sembrare un buffer invertente con enable, ma non sarebbe coerente con il circuito. Puoi spiegare?

-

Heavy

Heavy

565 1 5 - Utente disattivato per decisione dell'amministrazione proprietaria del sito

- Messaggi: 260

- Iscritto il: 28 dic 2013, 0:39

- Località: Conegliano Veneto

0

voti

Heavy ha scritto:Che porta è T3? Non ne ho mai viste disegnate così. Potrebbe sembrare un buffer invertente con enable, ma non sarebbe coerente con il circuito. Puoi spiegare?

L'ha scritto:

Candy ha scritto:[...]T3 sarà certamente interdetto, con 0 in base ed 1 in uscita, indipendentemente dallo stato di T3. Una sorta di Enable

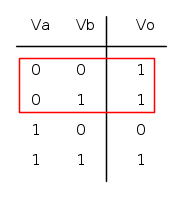

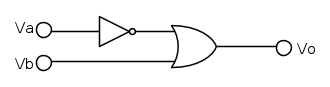

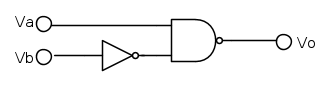

Non sono però d'accordo che un inverter con enable abbia sempre l'uscita a 1...di solito gli enable la staccano mandandola in alta impedenza. Credo che un equivalente logico più corretto (anche perché l'enable su una porta NOT non è previsto dall'algebra di Boole) per la tabella (ps: grazie

sia

o, per meglio dire (visto che la porta OR su silicio verrebbe come una NOR con un NOT in serie, così si risparmia un NOT):

_______________________________________________________

Gli oscillatori non oscillano mai, gli amplificatori invece sempre

Io HO i poteri della supermucca, e ne vado fiero!

Gli oscillatori non oscillano mai, gli amplificatori invece sempre

Io HO i poteri della supermucca, e ne vado fiero!

0

voti

obiuan ha scritto:L'ha scritto:Candy ha scritto:[...]T3 sarà certamente interdetto, con 0 in base ed 1 in uscita, indipendentemente dallo stato di T3. Una sorta di Enable

Hai ragione

-

Heavy

Heavy

565 1 5 - Utente disattivato per decisione dell'amministrazione proprietaria del sito

- Messaggi: 260

- Iscritto il: 28 dic 2013, 0:39

- Località: Conegliano Veneto

16 messaggi

• Pagina 2 di 2 • 1, 2

Chi c’è in linea

Visitano il forum: Nessuno e 74 ospiti

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)