Heavy

Heavy scusa l'enorme ritardo nella risposta ma solo oggi sto avendo finalmente il tempo di rivedere tutti i post che ho lasciato in sospeso. Vedo di chiarire un po' quello che voglio dire, partendo dal caso generale per arrivare al caso della famiglia RTL.

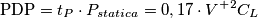

Abbiamo detto che il parametro PDP è definito a partire da due rilevanti grandezze caratteristiche per le prestazioni dei circuiti logici, essendo proprio quelle che permettono di valutare sia il livello di integrazione realizzabile, sia la massima velocità di operazione, ovvero il tempo di propagazione (o ritardo di propagazione) e la potenza dissipata, intesa come quella fornita dal circuito di alimentazione e che viene assorbita dalla porta logica generica nel suo funzionamento e di cui distinguiamo (come hai fatto correttamente notare) una componente

statica relativa all'assorbimento circuitale in assenza di commutazione logica, e una componente

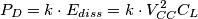

dinamica relativa all'assorbimento durante le transizioni da uno stato logico all'altro.

Abbiamo anche detto che, in generale, il miglioramento di una di queste due grandezze va a scapito dell'altra, sicché una riduzione della potenza dissipata comporta un aumento del tempo di propagazione e viceversa, portando il progettista a dover effettuare una scelta ottima.

Detto questo, considero un caso generale idealizzato, ossia un interruttore di una famiglia logica incognita X:

Il circuito è formato da un invertitore elementare basato su un interruttore controllato dal segnale di ingresso

(che idealizza il dispositivo attivo), caricato in uscita da una capacità

che modella sostanzialmente l'effetto di carico dei circuiti inseriti a valle dell'invertitore stesso (ad esempio gli stadi di ingresso delle porte logiche inserite in cascata). Essendo l'interruttore ideale, si assume che i tempi di apertura e chiusura siano istantanei e che ci sia una caduta di tensione perfettamente nulla quando il tasto è chiuso (condizione di cortocircuito).

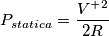

La potenza dissipata

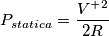

statica è in questo caso quella assorbita nello stato di uscita bassa, in quanto nello stato di uscita alta chiaramente non può circolare alcuna corrente; tale potenza vale per la precisione:

Il ritardo di propagazione dell'invertitore, considerando che il segnale applicato all'ingresso di controllo sia anch'esso idealizzato con tempi di salita e discesa perfettamente nulli, sarà funzione del solo tempo che impiega la capacità di carico

a caricarsi per mezzo di R, in quanto la scarica avviene in un tempo nullo attraverso l'interruttore chiuso in cortocircuito con il potenziale di riferimento. Il ritardo allora sarà proporzionale alla costante di tempo di carica

e dato dalla seguente espressione:

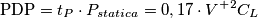

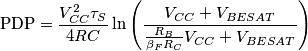

dal momento che, convenzionalmente, il ritardo di propagazione è proprio definito come valore medio tra i due tempi di transizione (alto -> basso e basso -> alto). A questo punto il parametro PDP è dato dalla relazione:

che risulta, come vedi, dipendente dalla sola tensione di alimentazione e dal carico capacitivo, ma non dalle caratteristiche dell'invertitore (in questo caso riconducibili al solo valore della resistenza). Il PDP (come anticipato nei post precedenti) è quindi un

fattore di merito dell'invertitore, nel senso che

più piccolo è, maggiore sarà la velocità di lavoro a parità di potenza dissipata, o minore sarà il consumo a parità di velocità operativa

:

Sempre come anticipato, il costruttore fornisce questo parametro o in forma numerica o con delle curve ritardo-potenza dissipata (normalmente in scala logaritmica sia per l'ascissa che per l'ordinata).

Chiarito questo, passiamo all'invertitore della famiglia logica RTL:

La dissipazione di potenza statica è nulla se l'ingresso è nello stato logico basso, perché ovviamente il transistor è in questo caso nello stato di interdizione; si ha invece consumo di potenza nello stato logico alto, dovuto alla corrente di saturazione che invece adesso circola nel transistore. Per compendiare queste due situazioni quindi, la dissipazione di potenza viene valutata mediando le potenze dissipate nei due possibili stati dell'invertitore e risulta:

dove

è la corrente di collettore nello stato di saturazione (opposto a quello di interdizione) e

è la tensione di uscita spillata al collettore allo stato basso (transistor saturo) che per i BJT si aggira intorno agli 0,2 volt, quindi lecitamente trascurabile in quella relazione.

Andiamo adesso ad analizzare il comportamento dinamico dell'invertitore RTL. Supponiamo che questo sia sollecitato da un segnale impulsivo di tipo logico (un gradino o un'onda quadra sostanzialmente). Per quantificare diamo dei valori reali a questo invertitore RTL. Ipotizziamo che il guadagno di corrente sia

,

,

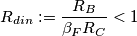

e il rapporto resistivo

. L'andamento della tensione d'uscita in funzione di quella di ingresso sarà conseguentemente:

Visto che hai nominato i MOS, come vedi la caratteristica d'uscita dell'RTL è effettivamente simile a quella presentata da un invertitore della famiglia MOS, ma con una

sostanziale differenza: in tal caso la tensione d'uscita passa dallo stato basso a quello alto dopo un tempo finito, durante il quale il BJT rimane ancora nello stato di saturazione, per un intervallo di tempo finito non nullo dopo che il segnale di ingresso è ritornato al livello basso. Questo tempo caratteristico (in figura indicato con

), prende il nome di

tempo di accumulo e si somma ai tempi di transizione

e

. Questo tempo d'accumulo è dovuto al tempo richiesto per smaltire la carica dei portatori minoritari accumulati in eccesso nella regione di base durante la condizione di saturazione (cerca nel forum qualche altro mio post dove ho trattato esattamente questa situazione, se vuoi) e contribuisce con una quota significativa al ritardo di propagazione delle porte bipolari operanti in regime di saturazione. L'analisi per ricavare le relazioni sui tempi è davvero molto lunga, ad ogni modo ci basta sapere che i tre tempi caratteristici dell'invertitore RTL (

,

e

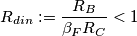

) sono legati alla dinamica di commutazione in funzione del seguente rapporto caratteristico:

che in buona sostanza assume un significato similare al fattore di forma per gli invertitori NMOS. Se indichiamo adesso con

il rapporto in tensione

, otteniamo le seguenti espressioni per i ritardi di propagazione:

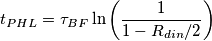

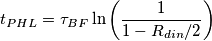

1)

;

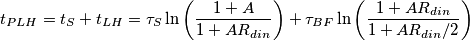

2)

;

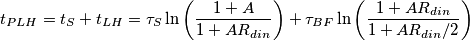

3)

![t_{P}=\frac{t_{PHL}+t_{PLH}}{2}=\frac{1}{2}\left \{\tau _{S}\ln\left ( \frac{1+A}{1+AR_{din}}\right ) +\tau _{BF}\ln\left [ \frac{1+AR_{din}}{(1+AR_{din}/2)(1-R_{din}/2)} \right ] \right \} t_{P}=\frac{t_{PHL}+t_{PLH}}{2}=\frac{1}{2}\left \{\tau _{S}\ln\left ( \frac{1+A}{1+AR_{din}}\right ) +\tau _{BF}\ln\left [ \frac{1+AR_{din}}{(1+AR_{din}/2)(1-R_{din}/2)} \right ] \right \}](/forum/latexrender/pictures/4ec98656ecb1f4f41ed0ec3836a11474.png)

di seguito plottate, assumendo per l'invertitore RTL i seguenti parametri:

,

,

e

:

Da questo grafico è chiaro come la riduzione del rapporto resistivo e cioè del forzamento in saturazione del BJT, se da una parte accelera le transizioni alto -> basso e basso -> alto, dall'altra aumento molto il tempo di accumulo, che diviene la parte più rilevante del ritardo di propagazione a forzamenti elevati (stesse considerazioni si possono fare anche per via analitica).

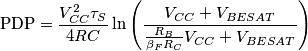

A questo punto il PDP è dato dal prodotto tra la

e la relazione 3); nell'ipotesi di forzamento significativo del dispositivo in saturazione, il maggior contributo al ritardo di propagazione è dato dal tempo di accumulo

e, saltando tutti i passaggi, si giunge alla seguente espressione approssimata del parametro:

da cui puoi vedere che, anche per l'invertitore bipolare, se il carico aumenta la dissipazione di potenza diminuisce, ma il ritardo di propagazione aumenta. In questo caso però,

diversamente da quanto accade negli invertitori MOS, il prodotto ritardo potenza non è indipendente dal valore del carico

, in quanto questo compare nell'espressione del ritardo sotto il logaritmico.

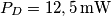

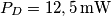

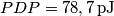

Per un invertitore RTL volendo dare un'ordine di grandezza al PDP, assumendo

,

,

, e con i valori del precedente grafico, si ottiene:

-

;

-

;

-

.

Quindi come vedi, ha senso moltiplicare il ritardo di propagazione (che compendia tempi di salita e di discesa) per la tensione di alimentazione e la corrente assorbita dalla porta ed è assolutamente estendibile dalla famiglia MOS alla famiglia RTL, con quelle precisazioni di cui ho parlato abbondantemente.

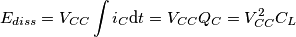

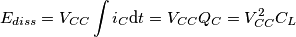

L'energia di commutazione non è esattamente quella usata per spostare le cariche di cui dicevo ma è

l'energia assorbita nel passaggio dallo stato basso a quello alto e vale:

(riprendendo in esame il caso dell'invertitore ideale). Questa energia dunque viene per metà dissipata nell'invertitore e per l'altra metà immagazzinata nella capacità, essendo questa, con il condensatore carico alla tensione di alimentazione, pari a

. Nel passaggio dallo stato alto a quello basso la capacità, scaricandosi, perde quell'energia immagazzinata, per cui l'energia totale persa nelle due transizioni sarà esattamente

e la potenza dissipata, assumendo che l'invertitore compia

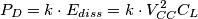

commutazioni nell'unità di tempo, vale:

![]() carloc,

carloc, ![]() g.schgor,

g.schgor, ![]() BrunoValente,

BrunoValente, ![]() IsidoroKZ

IsidoroKZ

(che idealizza il dispositivo attivo), caricato in uscita da una capacità

(che idealizza il dispositivo attivo), caricato in uscita da una capacità  che modella sostanzialmente l'effetto di carico dei circuiti inseriti a valle dell'invertitore stesso (ad esempio gli stadi di ingresso delle porte logiche inserite in cascata). Essendo l'interruttore ideale, si assume che i tempi di apertura e chiusura siano istantanei e che ci sia una caduta di tensione perfettamente nulla quando il tasto è chiuso (condizione di cortocircuito).

che modella sostanzialmente l'effetto di carico dei circuiti inseriti a valle dell'invertitore stesso (ad esempio gli stadi di ingresso delle porte logiche inserite in cascata). Essendo l'interruttore ideale, si assume che i tempi di apertura e chiusura siano istantanei e che ci sia una caduta di tensione perfettamente nulla quando il tasto è chiuso (condizione di cortocircuito).

a caricarsi per mezzo di R, in quanto la scarica avviene in un tempo nullo attraverso l'interruttore chiuso in cortocircuito con il potenziale di riferimento. Il ritardo allora sarà proporzionale alla costante di tempo di carica

a caricarsi per mezzo di R, in quanto la scarica avviene in un tempo nullo attraverso l'interruttore chiuso in cortocircuito con il potenziale di riferimento. Il ritardo allora sarà proporzionale alla costante di tempo di carica  e dato dalla seguente espressione:

e dato dalla seguente espressione:

:

:

è la corrente di collettore nello stato di saturazione (opposto a quello di interdizione) e

è la corrente di collettore nello stato di saturazione (opposto a quello di interdizione) e  è la tensione di uscita spillata al collettore allo stato basso (transistor saturo) che per i BJT si aggira intorno agli 0,2 volt, quindi lecitamente trascurabile in quella relazione.

è la tensione di uscita spillata al collettore allo stato basso (transistor saturo) che per i BJT si aggira intorno agli 0,2 volt, quindi lecitamente trascurabile in quella relazione. ,

,  ,

,  e il rapporto resistivo

e il rapporto resistivo  . L'andamento della tensione d'uscita in funzione di quella di ingresso sarà conseguentemente:

. L'andamento della tensione d'uscita in funzione di quella di ingresso sarà conseguentemente: ), prende il nome di tempo di accumulo e si somma ai tempi di transizione

), prende il nome di tempo di accumulo e si somma ai tempi di transizione  e

e  . Questo tempo d'accumulo è dovuto al tempo richiesto per smaltire la carica dei portatori minoritari accumulati in eccesso nella regione di base durante la condizione di saturazione (cerca nel forum qualche altro mio post dove ho trattato esattamente questa situazione, se vuoi) e contribuisce con una quota significativa al ritardo di propagazione delle porte bipolari operanti in regime di saturazione. L'analisi per ricavare le relazioni sui tempi è davvero molto lunga, ad ogni modo ci basta sapere che i tre tempi caratteristici dell'invertitore RTL (

. Questo tempo d'accumulo è dovuto al tempo richiesto per smaltire la carica dei portatori minoritari accumulati in eccesso nella regione di base durante la condizione di saturazione (cerca nel forum qualche altro mio post dove ho trattato esattamente questa situazione, se vuoi) e contribuisce con una quota significativa al ritardo di propagazione delle porte bipolari operanti in regime di saturazione. L'analisi per ricavare le relazioni sui tempi è davvero molto lunga, ad ogni modo ci basta sapere che i tre tempi caratteristici dell'invertitore RTL ( ,

,  e

e  ) sono legati alla dinamica di commutazione in funzione del seguente rapporto caratteristico:

) sono legati alla dinamica di commutazione in funzione del seguente rapporto caratteristico:

il rapporto in tensione

il rapporto in tensione  , otteniamo le seguenti espressioni per i ritardi di propagazione:

, otteniamo le seguenti espressioni per i ritardi di propagazione: ;

; ;

;![t_{P}=\frac{t_{PHL}+t_{PLH}}{2}=\frac{1}{2}\left \{\tau _{S}\ln\left ( \frac{1+A}{1+AR_{din}}\right ) +\tau _{BF}\ln\left [ \frac{1+AR_{din}}{(1+AR_{din}/2)(1-R_{din}/2)} \right ] \right \} t_{P}=\frac{t_{PHL}+t_{PLH}}{2}=\frac{1}{2}\left \{\tau _{S}\ln\left ( \frac{1+A}{1+AR_{din}}\right ) +\tau _{BF}\ln\left [ \frac{1+AR_{din}}{(1+AR_{din}/2)(1-R_{din}/2)} \right ] \right \}](/forum/latexrender/pictures/4ec98656ecb1f4f41ed0ec3836a11474.png)

,

,  ,

,  e

e  :

: e la relazione 3); nell'ipotesi di forzamento significativo del dispositivo in saturazione, il maggior contributo al ritardo di propagazione è dato dal tempo di accumulo

e la relazione 3); nell'ipotesi di forzamento significativo del dispositivo in saturazione, il maggior contributo al ritardo di propagazione è dato dal tempo di accumulo  e, saltando tutti i passaggi, si giunge alla seguente espressione approssimata del parametro:

e, saltando tutti i passaggi, si giunge alla seguente espressione approssimata del parametro:

, in quanto questo compare nell'espressione del ritardo sotto il logaritmico.

, in quanto questo compare nell'espressione del ritardo sotto il logaritmico. ,

,  ,

,  , e con i valori del precedente grafico, si ottiene:

, e con i valori del precedente grafico, si ottiene: ;

; ;

; .

.

. Nel passaggio dallo stato alto a quello basso la capacità, scaricandosi, perde quell'energia immagazzinata, per cui l'energia totale persa nelle due transizioni sarà esattamente

. Nel passaggio dallo stato alto a quello basso la capacità, scaricandosi, perde quell'energia immagazzinata, per cui l'energia totale persa nelle due transizioni sarà esattamente  e la potenza dissipata, assumendo che l'invertitore compia

e la potenza dissipata, assumendo che l'invertitore compia  commutazioni nell'unità di tempo, vale:

commutazioni nell'unità di tempo, vale: