Vi spiego le cose che credo fino ad ora mi sono chiare:

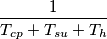

-Data una rete logica, per calcolare la frequenza massima di clock ammissibile dal circuito, devo calcolare la seguente formula

, con Tcp=tempo di crtical path, Tsu=tempo di setup del flip flop, Th=tempo di hold del flip flop.

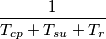

, con Tcp=tempo di crtical path, Tsu=tempo di setup del flip flop, Th=tempo di hold del flip flop.Ma perche spesso trovo discordanze su questa formula? a volte la trovo anche cosi:

, con Tr=tempo di ritardo del flip flop. Quale delle due formule devo usare?

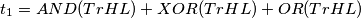

, con Tr=tempo di ritardo del flip flop. Quale delle due formule devo usare?-Per il calcolo del critical path, devo considerare il percorso che richiede più tempo giusto? (probabilmente quello che attraversa più porte logiche), in questo caso nel mio esercizio, attraverso: FF1-AND-XOR-OR-FF2, considerando sempre il fatto che se in una porta logica invertente se entra un segnale tipo LH, uscirà un segnale HL; mentre una porta logica "normale", entra HL ed esce HL; mentre per la porta "xor" devo considerare entrambi i casi. Quindi in questo esercizio otengo:

teoricamente dovrei anche calcolarmi t3 e t4 con la AND(Tr LH), ma già si nota che se facessi cosi sarebbe inutile dato che devo considerare i tempi più grandi che mi vengono dati da AND(Tr HL). Devo considerare i tempi più grandi infatti giusto?

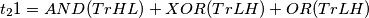

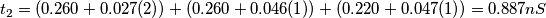

teoricamente dovrei anche calcolarmi t3 e t4 con la AND(Tr LH), ma già si nota che se facessi cosi sarebbe inutile dato che devo considerare i tempi più grandi che mi vengono dati da AND(Tr HL). Devo considerare i tempi più grandi infatti giusto?-All'interno della formula, devo anche considerare il "load factor" che sarebbe il fattore di carico della porta successiva, quindi (calcolo direttamente t2 dato che è quella con tempo più grande):

ora qui ho un paio di domande riguardanti il fattore di carico:

1) In teoria dopo l'ultima OR, il fattore di carico non dovrebbe essere 4? dato che il FF2 ha appunto fattore di carico=4.

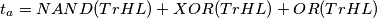

2)Mettiamo il caso che avessi considerato un altro percorso come ad esempio FF1-NAND-XOR-OR-FF2, in questo caso avrei:

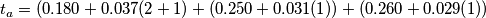

, con tutti i vari casi, quindi considerando solo questo caso avrei:

, con tutti i vari casi, quindi considerando solo questo caso avrei:  . Cioè dopo la prima NAND nel load factor devo fare la somma delle porte successive collegate ad essa, cioè della XOR e della NOR, giusto?

. Cioè dopo la prima NAND nel load factor devo fare la somma delle porte successive collegate ad essa, cioè della XOR e della NOR, giusto?-Ora facendo il calcolo della t1 precedente, che era

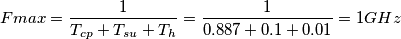

, mi posso anche calcolare la massima frequenza di clock ammissibile dal circuito usando questa formula:

, mi posso anche calcolare la massima frequenza di clock ammissibile dal circuito usando questa formula: .

.Ringrazio in anticipo per gli eventuali chiarimenti

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)

. Questo vuol dire semplicemente che misuro i ritardi a partire da un fronte che scelgo io.

. Questo vuol dire semplicemente che misuro i ritardi a partire da un fronte che scelgo io.  che e` arrivato il fronte, l'uscita del primo flip flop cambia e

che e` arrivato il fronte, l'uscita del primo flip flop cambia e  .

. , altrimenti il secondo flip flop si incasina (stati metastabili o peggio). Questo vuol dire che il fronte di clock successivo non puo` arrivare contemporaneamente ai dati, ma deve arrivare

, altrimenti il secondo flip flop si incasina (stati metastabili o peggio). Questo vuol dire che il fronte di clock successivo non puo` arrivare contemporaneamente ai dati, ma deve arrivare  non

non

.

.