Massima frequenza di clock e critical path

Moderatori: ![]() carloc,

carloc, ![]() g.schgor,

g.schgor, ![]() BrunoValente,

BrunoValente, ![]() IsidoroKZ

IsidoroKZ

20 messaggi

• Pagina 2 di 2 • 1, 2

0

voti

Sono in vacanza e scrivo dal telefono, quindi sarò brevissimo, ma non è vero che c'è un solo ritardo. Ci sono contamination delay e propagation delay. Quello rilevante per il tuo problema è il secondo. Il primo è importante per la condizione di hold.

0

voti

Usa il tasto RISPONDI, non il tasto CITA!

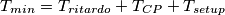

Per il calcolo della , non pensare alla frequenza ma pensa al periodo di clock minimo affinchè il circuito non vada in violazione dei vari tempi di ritardo (parola qui usata in modo generico).

, non pensare alla frequenza ma pensa al periodo di clock minimo affinchè il circuito non vada in violazione dei vari tempi di ritardo (parola qui usata in modo generico).

Ovvero

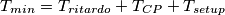

dove il periodo minimo sarà una somma dei vari tempo di ritardo:

I tempi di ritardo che devi prendere in considerazione sono i seguenti:

Tempo di ritardo del Flip Flop, ovvero il tempo necessario affinche tutti i Flip Flop forniscano in uscita un segnale stabile. (qualche Flip Flop potrebbe fare anche prima degli altri ma ovviamente bisogna "aspettare l'ultimo affinchè il dato sia consistente)

Tempo di ritardo del Flip Flop, ovvero il tempo necessario affinche tutti i Flip Flop forniscano in uscita un segnale stabile. (qualche Flip Flop potrebbe fare anche prima degli altri ma ovviamente bisogna "aspettare l'ultimo affinchè il dato sia consistente)

Tempo di Critical Path, ovvero il tempo necessario a tutto blocco di logica combinatoria affinchè il segnale di uscita prodotto sia stabile e consistente. Essendoci vari percorsi possibili, alcuni ci mettono meno tempo degli altri ma comunque affinchè il segnale di uscita sia consistente bisogna aspettare l'ultimo, ecco perché Critical Path. Il tempo dopo il quale la logica inizia a generare il segnale di uscita (dando in uscita segnali non consistenti) è detto invece Best Path.

Tempo di Critical Path, ovvero il tempo necessario a tutto blocco di logica combinatoria affinchè il segnale di uscita prodotto sia stabile e consistente. Essendoci vari percorsi possibili, alcuni ci mettono meno tempo degli altri ma comunque affinchè il segnale di uscita sia consistente bisogna aspettare l'ultimo, ecco perché Critical Path. Il tempo dopo il quale la logica inizia a generare il segnale di uscita (dando in uscita segnali non consistenti) è detto invece Best Path.

Tempo setup, ovvero tempo per il quale il segnale deve essere stabile prima della successiva transisione del clock. Questo significa che dopo tale tempo è già possibile (ma ovviamente non obbligatorio) far commutare il clock, ed è quindi il tempo di setup che impone l'ultimo limite al periodo minimo.

Tempo setup, ovvero tempo per il quale il segnale deve essere stabile prima della successiva transisione del clock. Questo significa che dopo tale tempo è già possibile (ma ovviamente non obbligatorio) far commutare il clock, ed è quindi il tempo di setup che impone l'ultimo limite al periodo minimo.

Dunque:

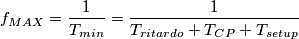

Da cui la giustificazione alla formula:

Per il calcolo della

, non pensare alla frequenza ma pensa al periodo di clock minimo affinchè il circuito non vada in violazione dei vari tempi di ritardo (parola qui usata in modo generico).

, non pensare alla frequenza ma pensa al periodo di clock minimo affinchè il circuito non vada in violazione dei vari tempi di ritardo (parola qui usata in modo generico).Ovvero

dove il periodo minimo sarà una somma dei vari tempo di ritardo:

I tempi di ritardo che devi prendere in considerazione sono i seguenti:

Tempo di ritardo del Flip Flop, ovvero il tempo necessario affinche tutti i Flip Flop forniscano in uscita un segnale stabile. (qualche Flip Flop potrebbe fare anche prima degli altri ma ovviamente bisogna "aspettare l'ultimo affinchè il dato sia consistente)

Tempo di ritardo del Flip Flop, ovvero il tempo necessario affinche tutti i Flip Flop forniscano in uscita un segnale stabile. (qualche Flip Flop potrebbe fare anche prima degli altri ma ovviamente bisogna "aspettare l'ultimo affinchè il dato sia consistente) Tempo di Critical Path, ovvero il tempo necessario a tutto blocco di logica combinatoria affinchè il segnale di uscita prodotto sia stabile e consistente. Essendoci vari percorsi possibili, alcuni ci mettono meno tempo degli altri ma comunque affinchè il segnale di uscita sia consistente bisogna aspettare l'ultimo, ecco perché Critical Path. Il tempo dopo il quale la logica inizia a generare il segnale di uscita (dando in uscita segnali non consistenti) è detto invece Best Path.

Tempo di Critical Path, ovvero il tempo necessario a tutto blocco di logica combinatoria affinchè il segnale di uscita prodotto sia stabile e consistente. Essendoci vari percorsi possibili, alcuni ci mettono meno tempo degli altri ma comunque affinchè il segnale di uscita sia consistente bisogna aspettare l'ultimo, ecco perché Critical Path. Il tempo dopo il quale la logica inizia a generare il segnale di uscita (dando in uscita segnali non consistenti) è detto invece Best Path. Tempo setup, ovvero tempo per il quale il segnale deve essere stabile prima della successiva transisione del clock. Questo significa che dopo tale tempo è già possibile (ma ovviamente non obbligatorio) far commutare il clock, ed è quindi il tempo di setup che impone l'ultimo limite al periodo minimo.

Tempo setup, ovvero tempo per il quale il segnale deve essere stabile prima della successiva transisione del clock. Questo significa che dopo tale tempo è già possibile (ma ovviamente non obbligatorio) far commutare il clock, ed è quindi il tempo di setup che impone l'ultimo limite al periodo minimo.Dunque:

Da cui la giustificazione alla formula:

0

voti

Scusate se mi intrometto. Anche io ho dei dubbi sullo stesso argomento.

Non so se conviene creare un'altra discussione. Nel caso, ditemelo!

Il mio dubbio riguarda il tempo di ritardo da ALTO a BASSO o da BASSO a ALTO. Quali prendere in considerazione nel calcolo della frequenza massima?

Per il flip flop, va considerato il tempo di ritardo da ALTO a BASSO o quello da BASSO a ALTO? E perché?

P.S. #guestleandro11 anche tu alle prese con Berta, eh?!?

Non so se conviene creare un'altra discussione. Nel caso, ditemelo!

Il mio dubbio riguarda il tempo di ritardo da ALTO a BASSO o da BASSO a ALTO. Quali prendere in considerazione nel calcolo della frequenza massima?

Per il flip flop, va considerato il tempo di ritardo da ALTO a BASSO o quello da BASSO a ALTO? E perché?

P.S. #guestleandro11 anche tu alle prese con Berta, eh?!?

0

voti

Le condizioni devono essere soddisfatte sempre, indipendentemente dai dati in ingesso. Quindi per la frequenza (setup) il tempo più lungo. Per la condizione di hold, invece, quello più corto.

Boiler

Boiler

0

voti

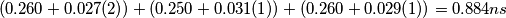

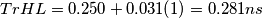

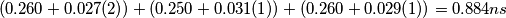

Ciao ragazzi quindi credo di avere trovato la soluzione.

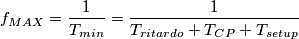

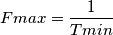

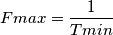

Allora la frequenza massima è data da .

.

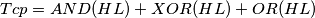

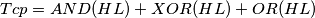

Per calcolare quindi , devo sommare il Tempo di crtical path che riguarda la logica combinatoria, il Tempo di setup del flip flop che riceve il dato (quello a destra), il Tempo di ritardo del flip flop che invia il dato (il primo quello a sinistra).

, devo sommare il Tempo di crtical path che riguarda la logica combinatoria, il Tempo di setup del flip flop che riceve il dato (quello a destra), il Tempo di ritardo del flip flop che invia il dato (il primo quello a sinistra).

Quindi:

=

=

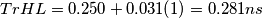

-Ora devo calcolare il tempo di ritardo che riguarda solo il primo flip flop cioè

-Ora calcolo il il tempo di set-up che riguarda il secondo flip flop

Infine faccio la somma di tutti e tre questi tempi e ottengo il tempo minimo. Ma dovrei considerare anche il tempo di hold necessario affinche il secondo flip flop è in grado di elaborare i dati in modo efficace? (cioè il tempo che il dato rimane stabile dopo il fronte del clock).

Allora la frequenza massima è data da

.

.Per calcolare quindi

, devo sommare il Tempo di crtical path che riguarda la logica combinatoria, il Tempo di setup del flip flop che riceve il dato (quello a destra), il Tempo di ritardo del flip flop che invia il dato (il primo quello a sinistra).

, devo sommare il Tempo di crtical path che riguarda la logica combinatoria, il Tempo di setup del flip flop che riceve il dato (quello a destra), il Tempo di ritardo del flip flop che invia il dato (il primo quello a sinistra).Quindi:

=

=

-Ora devo calcolare il tempo di ritardo che riguarda solo il primo flip flop cioè

-Ora calcolo il il tempo di set-up che riguarda il secondo flip flop

Infine faccio la somma di tutti e tre questi tempi e ottengo il tempo minimo. Ma dovrei considerare anche il tempo di hold necessario affinche il secondo flip flop è in grado di elaborare i dati in modo efficace? (cioè il tempo che il dato rimane stabile dopo il fronte del clock).

-

guestleandro11

guestleandro11

10 1 2 - Messaggi: 8

- Iscritto il: 17 lug 2015, 19:06

0

voti

guestleandro11 ha scritto:Ma dovrei considerare anche il tempo di hold necessario affinche il secondo flip flop è in grado di elaborare i dati in modo efficace? (cioè il tempo che il dato rimane stabile dopo il fronte del clock).

Pensaci un po'... se anche rallenti il clock fino allo spasimo, cambia qualcosa per la condizione di hold?

Boiler

0

voti

mmmm giusto non cambierebbe nulla. Quindi è risolto nel modo giusto l'esercizio, puoi confermare?

-

guestleandro11

guestleandro11

10 1 2 - Messaggi: 8

- Iscritto il: 17 lug 2015, 19:06

0

voti

Nel caso avesse considerato il percorso : FF1-NAND-XOR-OR-FF2

il carico da considerare su XOR sarebbe quello complessivo di tutte le unità logiche collegate ad esso , cioè il fattore di carico 2 dello XOR, 1 del NOR e 1 dell' OR e 4 del Flip_Flop2 , cioè 8 giusto ?

(lo chiedo perché in un commento precedente ho visto che era stato scritto (2+1) invece che (2+1+1+4).

Se il ragionamento è questo, perché nel calcolo del tempo di ritardo del primo Flip_Flop si considera come carico solamente l' AND ? Forse perché in realtà ci sono 3 Flip_Flop all'inizio ciascuno collegato ad uno dei tre elementi logici iniziali e non un solo Flip_Flop come sembrerebbe ?

Allo stesso modo perché l'OR finale vede come carico 1 e non il 4 del Flip_Flop ?

Grazie..

il carico da considerare su XOR sarebbe quello complessivo di tutte le unità logiche collegate ad esso , cioè il fattore di carico 2 dello XOR, 1 del NOR e 1 dell' OR e 4 del Flip_Flop2 , cioè 8 giusto ?

(lo chiedo perché in un commento precedente ho visto che era stato scritto (2+1) invece che (2+1+1+4).

Se il ragionamento è questo, perché nel calcolo del tempo di ritardo del primo Flip_Flop si considera come carico solamente l' AND ? Forse perché in realtà ci sono 3 Flip_Flop all'inizio ciascuno collegato ad uno dei tre elementi logici iniziali e non un solo Flip_Flop come sembrerebbe ?

Allo stesso modo perché l'OR finale vede come carico 1 e non il 4 del Flip_Flop ?

Grazie..

0

voti

Errata corrige :

ummo89 ha scritto:il carico da considerare su NAND sarebbe quello....

0

voti

Credo di essere arrivato alla giusta conclusione:

Per il FF1 abbiamo :

Il FF1 pilota un ingresso della NOR, 2 ingressi della NAND e 2 della AND,quindi

Load factor= 2xNAND+2xAND+NOR=2x1+2x1+1.

Per il resto la NAND vede come carichi la XOR la NOR e la OR e il FLIP FLOP 2

La OR come carico vede il FLIP FLOP 2 cioè Load Factor = 4.

Per il FF1 abbiamo :

Il FF1 pilota un ingresso della NOR, 2 ingressi della NAND e 2 della AND,quindi

Load factor= 2xNAND+2xAND+NOR=2x1+2x1+1.

Per il resto la NAND vede come carichi la XOR la NOR e la OR e il FLIP FLOP 2

La OR come carico vede il FLIP FLOP 2 cioè Load Factor = 4.

20 messaggi

• Pagina 2 di 2 • 1, 2

Chi c’è in linea

Visitano il forum: Nessuno e 39 ospiti

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)