da

da  elfo » 10 apr 2023, 18:27

elfo » 10 apr 2023, 18:27

Non credo di poter aggiungere molto a quanto gia' scritto - le idee mi sono venute solo DOPO avere letto i post prececenti

Solo due chiose su un punto gia' messo in evidenza in vari post

Etemenanki

Etemenanki post [10]

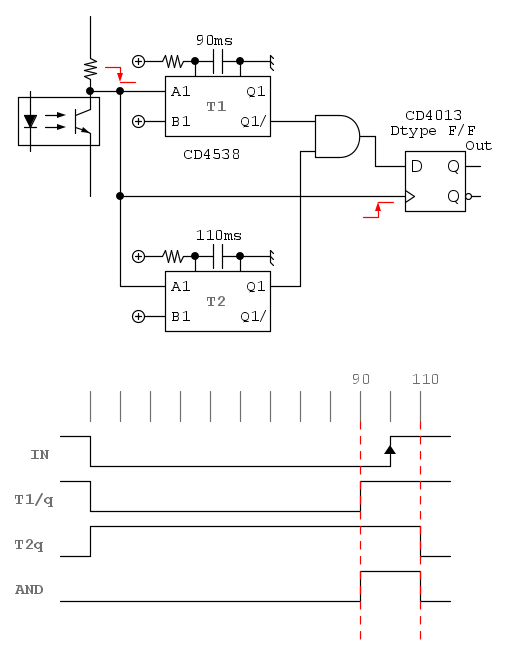

la rete RC sull'ingresso della AND serve a compensare il ritardo di propagazione delle 3 porte, monostabile piu inverter, altrimenti si avrebbe un'impulso molto breve in uscita all'arrivo dell'impulso di ingresso, il tempo puo anche essere inferiore, basta solo che sia superiore al ritardo di propagazione delle 3 porte

ThEnGi

ThEnGi post [12]

Rete R3 C3 nello schema ha la stessa funzione descritta da Etemenanki.

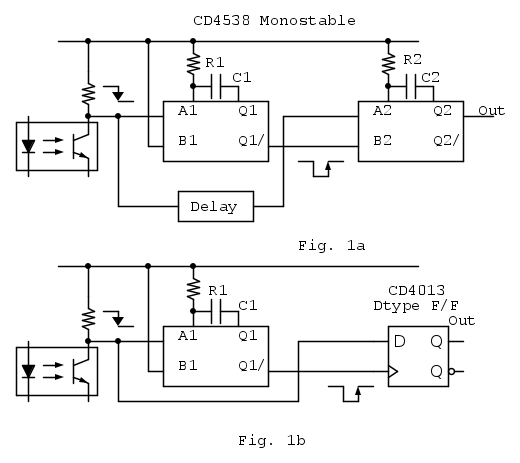

Nello schema seguente Fig. 1a ho "semplificato" lo schema del post [10] utilizzando un monostabile (come suggerito da

djnz

djnz) al posto delle porte logiche - in questo modo l'impostazione dei tempi e' piu' prevedibile (entro il 10% richiesto) dati i valori di R e C.

Il rettangolo "Delay" puo' essere un RC oppure una serie di porte logiche (od altro) ed assolve alla funzione descritta da Etemenanki.

L'uscita del circuito (se la durata del segnale in ingresso e' > R1C1) e' in impulso di durata R2C2.

Per ovviare alla necessita' di introdurre un ritardo si puo' utilizzare il circuito di Fig. 1b - rielaborazione del circuito del post [12].

La differenza e' la sostituzione del F/F S/R con un F/F Dtype.

In questo modo non e' necessario introdurre un ritardo perche' il livello presente sull'ingresso D viene trasferito all'uscita solo sul fronte di salita del clock.

L'uscita del circuito (se la durata del segnale in ingresso e' > R1C1) e' un livello che rimane attivo finche' il F/F non viene resettato.

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)