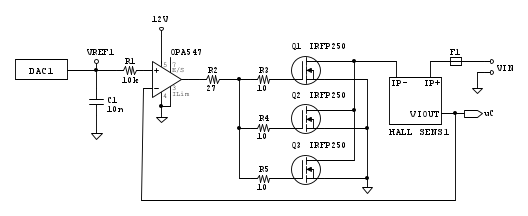

La frequenza di taglio del sensore di Hall coincide con la banda del sistema, forse potrebbe rompere un po' le scatole... Credo convenga ridurre il guadagno d'anello per farlo tagliare prima ed evitare instabilità.

Etemenanki ha scritto:Dovessi usare questi mosfet, con 3 in parallelo ed un buon dissipatore dovresti poter usare il carico anche intorno ai 100A senza che ti causi alcun problema, perche' data la suddivisione della corrente, con 3 mosfet ogni mosfet dovrebbe dissipare un nono della potenza in calore

Idealmente si, purtroppo però quando si parallelizzano MOSFET di potenza c'è un effetto abbastanza subdolo che fa andare in breakdown termico un die in tempo zero (si chiama

Spirito effect).

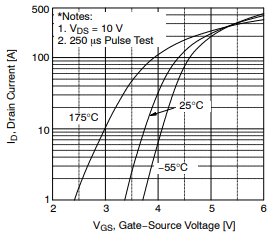

In poche parole quello che succede è che, da una certa tensione

in giù (detta di ZTC o Zero Thermal Coefficient), la tensione di soglia del MOS decresce con la temperatura più di quanto cresca la resistenza di canale, determinando un aumento della corrente di drain man mano che il silicio si scalda. Ovviamente questo produce un feedback positivo: più un singolo MOS conduce, più scalda, più tenderà a condurre, finché supera la SOA ed esplode.

- Ids_vs_Vgs_T_FDH055N15A.PNG (28.67 KiB) Osservato 3511 volte

In pratica siamo convinti che mettendo in parallelo

MOSFET la corrente si distribuisca (a meno delle variabilità di processo) in modo più o meno simile; in realtà, quando siamo a

sufficientemente bassa (come quando vogliamo usarlo in zona saturazione), nel giro di millisecondi uno dei MOS decide di punto in bianco che è giunto il momento di condurre un po' di più; complice un piccolo squilibrio termico e/o una

più alta, inizia a portare un po' più corrente: questo comporterà un aumento della sua temperatura di giunzione rispetto agli altri, la quale richiamerà ancora più corrente di prima finché il povero MOS si ritroverà per intero tutta la corrente di carico.

Nel caso di un singolo MOS ci pensa la retroazione del sistema a mantenere la corrente entro i limiti accettabili, ma nel caso di due MOS in parallelo molto sbilanciati non c'è nulla che impedisca a uno dei due di innescare questo meccanismo.

Questo effetto non si ritrova solo in più componenti diversi posti in parallelo, ma anche per i die all'interno dello stesso package: soprattutto per i MOSFET più recenti, che sono formati da più celle interconnesse all'interno di un unico package, questo effetto fa ridurre la SOA effettiva anche se il silicio di per sè potrebbe sopportarlo se fosse idealmente tutto alla stessa temperatura.

Le costanti di tempo sono così ridicole (10/100 us) che è praticamente impossibile intervenire tempestivamente.

Per questo motivo i MOSFET per applicazioni switching (la maggior parte dei recenti) hanno una pessima reazione se parallelizzati per un utilizzo lineare: per quel che ne so i MOSFET più vecchiotti si comportano meglio per queste applicazioni (hanno sempre il problema dello ZTC ma la variazione di corrente è molto più contenuta).

In questo caso io consiglierei di investire un po' di più sul MOS e scegliere un modello che sia adatto per un utilizzo lineare (so che li fa ad esempio la Littelfuse), dopodichè puoi parallelizzare tranquillamente un paio di questi badando bene però a mantenerli il più possibile alla stessa temperatura, ad esempio montandoli tutti sullo stesso dissipatore e raffreddando il tutto con una ventola.

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)

in giù (detta di ZTC o Zero Thermal Coefficient), la tensione di soglia del MOS decresce con la temperatura più di quanto cresca la resistenza di canale, determinando un aumento della corrente di drain man mano che il silicio si scalda. Ovviamente questo produce un feedback positivo: più un singolo MOS conduce, più scalda, più tenderà a condurre, finché supera la SOA ed esplode.

in giù (detta di ZTC o Zero Thermal Coefficient), la tensione di soglia del MOS decresce con la temperatura più di quanto cresca la resistenza di canale, determinando un aumento della corrente di drain man mano che il silicio si scalda. Ovviamente questo produce un feedback positivo: più un singolo MOS conduce, più scalda, più tenderà a condurre, finché supera la SOA ed esplode.  MOSFET la corrente si distribuisca (a meno delle variabilità di processo) in modo più o meno simile; in realtà, quando siamo a

MOSFET la corrente si distribuisca (a meno delle variabilità di processo) in modo più o meno simile; in realtà, quando siamo a  più alta, inizia a portare un po' più corrente: questo comporterà un aumento della sua temperatura di giunzione rispetto agli altri, la quale richiamerà ancora più corrente di prima finché il povero MOS si ritroverà per intero tutta la corrente di carico.

più alta, inizia a portare un po' più corrente: questo comporterà un aumento della sua temperatura di giunzione rispetto agli altri, la quale richiamerà ancora più corrente di prima finché il povero MOS si ritroverà per intero tutta la corrente di carico.