Clock Recovery con PLL

Moderatori: ![]() carloc,

carloc, ![]() g.schgor,

g.schgor, ![]() BrunoValente,

BrunoValente, ![]() IsidoroKZ

IsidoroKZ

12 messaggi

• Pagina 1 di 2 • 1, 2

0

voti

Allora non riesco a capire il funzionamento del PLL per il recupero del clock. Supponiamo di avere un PLL con comparatore di fase, filtro passa-basso, amplificatore e VCO con retroazione negativa e che voglia sincronizzare due clocl differenti, uno in trasmissione TX e uno in ricezione RX. Il PLL prende la fase del segnale d'ingresso e quella del segnale d'uscita, poi tramite il comparatore di fase produce un segnale di tensione proporzionale alla differenza di fase che rappresenta l'errore delle due fasi. Il filtro passa-passo determina una media dell'errore eliminando eventuali componenti spurie, l'amplificatore amplifica il segnale al fine di aumentare la precisione. Quindi il segnale arriva al VCO e la tensione che mi rappresenta l'errore forza il VCO a produrre una frequenza d'uscita che verrà riportata in ingresso per essere nuovamente comparata. A regime la frequenza d'uscita dal VCO sarà uguale a quella d'ingresso. Pertanto collegando in ingresso il TX e in uscita RX ottengo la sincronizzazione dei due clock. Però non ho ben capito per quale motivo a regime l'errore tende ad annullarsi, cioè come fa il VCO ad annullare l'errore? Ogni volta produce una frequenza minore o maggiore che so avvicina sempre di più a quella d'ingresso?

0

voti

Ciao  ireon.

ireon.

Per maggiore chiarezza, conviene che tu faccia uno schema del circuito a cui ti riferisci, anche uno schema a blocchi penso sia sufficente.

Per fare lo schema usa FIDOCADJ, al seguente link trovi una guida all' uso:

http://www.electroyou.it/elettrodomus/w ... -per-tonni

Per maggiore chiarezza, conviene che tu faccia uno schema del circuito a cui ti riferisci, anche uno schema a blocchi penso sia sufficente.

Per fare lo schema usa FIDOCADJ, al seguente link trovi una guida all' uso:

http://www.electroyou.it/elettrodomus/w ... -per-tonni

2

voti

ireon ha scritto:per quale motivo a regime l'errore tende ad annullarsi

perché come ogni sistema reale che esista su questa terra, anche il PLL ha una sua risposta temporale (o dualmente in frequenza) che consiste sempre in un transitorio e in un regime permanente. Bisogna capire come si evolva verso la condizione di equilibrio, dipendentemente dall'ordine del sistema (se è di primo ordine il transitorio evolve in un certo modo, se è di secondo ordine in un altro, ecc.) ed anche dal tipo di sollecitazione.

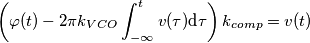

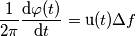

Ora il VCO è in effetti un modulatore di frequenza e il suo scopo, come hai correttamente detto, è fornire in uscita un segnale la cui frequenza (istantanea) sia proporzionale alla tensione di comando. Io non so il livello della trattazione con cui stai affrontando l'argomento, però io (penso) di fartelo capire analiticamente. Si dimostra che la funzione di trasferimento di un VCO ideale è la seguente:

![y(t)=Y\cdot \text{sgn}\left [\cos \left (2\pi \left (f_{VCO}t+k_{VCO}\int_{-\infty }^{t}v(\tau )\text{d}\tau \right ) \right ) \right ] y(t)=Y\cdot \text{sgn}\left [\cos \left (2\pi \left (f_{VCO}t+k_{VCO}\int_{-\infty }^{t}v(\tau )\text{d}\tau \right ) \right ) \right ]](/forum/latexrender/pictures/e8409f239b22da75508d7d5f47439ee3.png)

dove

è la frequenza di lavoro in assenza di oscillazione in ingresso (cioè in evoluzione libera quando v = 0);

è la frequenza di lavoro in assenza di oscillazione in ingresso (cioè in evoluzione libera quando v = 0);  è invece l'indice di modulazione che fornisce l'informazione sulla "profondità" della modulazione esercitata dal VCO in presenza di un ingresso canonico (ad esempio un gradino), ossia in altre parole la deviazione di frequenza del VCO indotto da una tensione di comando unitaria.

è invece l'indice di modulazione che fornisce l'informazione sulla "profondità" della modulazione esercitata dal VCO in presenza di un ingresso canonico (ad esempio un gradino), ossia in altre parole la deviazione di frequenza del VCO indotto da una tensione di comando unitaria. Piccola precisazione: per renderci conto che in questa relazione compare la frequenza istantanea, basta fare la derivata temporale dell'argomento di y(t):

![f_{i}(t)=\frac{1}{2\pi }\frac{\mathrm{d} }{\mathrm{d} t}\text{arg}[y(t)]=f_{VCO}+k_{VCO}v(t) f_{i}(t)=\frac{1}{2\pi }\frac{\mathrm{d} }{\mathrm{d} t}\text{arg}[y(t)]=f_{VCO}+k_{VCO}v(t)](/forum/latexrender/pictures/f127f2fbc0050206438a58d6a2f81ab0.png)

Consideriamo ora lo schema base che hai indicato tu, cioè quello ad anello chiuso con comparatore, filtro ed amplificatore; per semplicità (e che comunque non lede la generalità, visto che stiamo spiegando soltanto come evolve il VCO) supponiamo che nella catena non c'è il filtro passa basso, così che l'intero sistema in catena chiusa sia del primo ordine. Supponiamo che inizialmente la frequenza di oscillazione libera del VCO sia identica al segnale originale f0, per cui

; si deve anche assumere che la deviazione di fase in ingresso al comparatore sia piccola in modo da rientrare nella zona lineare della sua trans-caratteristica:

; si deve anche assumere che la deviazione di fase in ingresso al comparatore sia piccola in modo da rientrare nella zona lineare della sua trans-caratteristica:cioè dobbiamo ricadere nell'intervallo che ho evidenziato in rosso; in formule significa avere

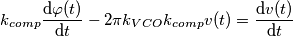

. Visto che manca il filtro, l'uscita del comparatore di fase è l'ingresso del VCO per cui ho:

. Visto che manca il filtro, l'uscita del comparatore di fase è l'ingresso del VCO per cui ho:

differenziando:

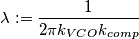

Se definisco la costante:

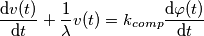

ottengo la seguente equazione differenziale del primo ordine che governa il funzionamento del PLL (di primo ordine):

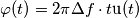

Adesso arriva in ingresso il nostro bel segnale affetto da uno scarto di frequenza tale da "rompere" il sincronismo con la frequenza del VCO; supponiamo che l'ingresso sia canonico, ad esempio un gradino unitario u(t); si ha:

da cui

Per le semplificazioni che abbiamo fatto, l'uscita del PLL è l'ingresso del VCO e la forma d'onda si trova risolvendo l'equazione differenziale che ho scritto sopra, in presenza di una forzante rappresentata dal gradino unitario (o meglio la sua derivata temporale):

![v(t)=\frac{\Delta f}{k_{VCO}}[1-e^{-t/\lambda }] v(t)=\frac{\Delta f}{k_{VCO}}[1-e^{-t/\lambda }]](/forum/latexrender/pictures/82ec9f24db5bbc9ac96f6be509badb10.png)

che ha il classico andamento esponenziale visto e stra-visto ad esempio nei circuiti di carica e scarica R-C / R-L; in questo caso , il raggiungimento dell'equilibrio avviene con andamento aperiodico di questo tipo (sempre per il fatto che il sistema ha molteplicità unitaria e la sollecitazione è un segnale di ordine zero):

Quindi cosa succede? Succede che il sistema raggiunge con andamento esponenziale e costante

il nuovo punto di equilibrio e all’uscita del comparatore la tensione si mantiene costante a quel valore che basta per spostare la frequenza del VCO:

il nuovo punto di equilibrio e all’uscita del comparatore la tensione si mantiene costante a quel valore che basta per spostare la frequenza del VCO:

Ora per capire circuitalmente cosa succede nel VCO è un bel macello; per semplificare, all'ingresso del VCO c'e' un circuito integratore realizzato con un ampl. operazionale, che tende a mantenere l'ingresso invertente ad una tensione uguale a quella dell'ingresso non invertente: cerca quindi di contrastare l'azione della reazione. A questo circuito segue un trigger di Smith il cui morsetto invertente è collegato all'uscita del primo operazionale. Il trigger trasforma il segnale uscito dall'integratore in una tensione ben definita: tale tensione varia tra due valori di tensione a seconda che l'ingresso superi una certa soglia o sia inferiore ad una seconda soglia, minore della prima. Poi ci sono dentro altre millemilacose da considerare, ma terra terra funge in questo modo.

Quindi è questa "opposizione" alla reazione che fa "adattare" (non è il termine adatto) il VCO allo shift

di frequenza imposto dalla tensione di controllo, sempre che sia garantita quella condizione iniziale di piccolo scarto (che dà poi origine al cosidetto intervallo di tenuta).

di frequenza imposto dalla tensione di controllo, sempre che sia garantita quella condizione iniziale di piccolo scarto (che dà poi origine al cosidetto intervallo di tenuta).Quindi non è che il VCO azzera l'errore magicamente, ma ogniqualvolta si presenta un ingresso con scarto di frequenza, c'è un corrispondente "adattamento" o a quest'ultimo da parte del VCO, o meglio insegue continuamente la nuova situazione, raggiungendo ogni qualvolta un regime permanente dove l'errore è nullo (come puoi vedere dall'ultima figura).

Non so se ho ben interpretato il tuo dubbio...

"Lo scienziato descrive ciò che esiste, l'ingegnere crea ciò che non era mai stato."

(T. von Kármán)

(T. von Kármán)

0

voti

In buona sostanza è un servomeccanismo con azione proporzionale e integrativa (PI)?

"La follia sta nel fare sempre la stessa cosa aspettandosi risultati diversi".

"Parla soltanto quando sei sicuro che quello che dirai è più bello del silenzio".

Rispondere è cortesia, ma lasciare l'ultima parola ai cretini è arte.

"Parla soltanto quando sei sicuro che quello che dirai è più bello del silenzio".

Rispondere è cortesia, ma lasciare l'ultima parola ai cretini è arte.

-

TardoFreak

TardoFreak

73,9k 8 12 13 - -EY Legend-

- Messaggi: 15754

- Iscritto il: 16 dic 2009, 11:10

- Località: Torino - 3° pianeta del Sistema Solare

0

voti

"Lo scienziato descrive ciò che esiste, l'ingegnere crea ciò che non era mai stato."

(T. von Kármán)

(T. von Kármán)

0

voti

Allora  TardoFreak la tua domanda mi ha incuriosito ed è in effetti totalmente attinente per cui mi son voluto documentare in merito dal momento che non ho mai affrontato il PLL da un punto di vista "sistemistico" o "controllistico".

TardoFreak la tua domanda mi ha incuriosito ed è in effetti totalmente attinente per cui mi son voluto documentare in merito dal momento che non ho mai affrontato il PLL da un punto di vista "sistemistico" o "controllistico".

Effettivamente la domanda è più che lecita perché, per via delle semplificazioni che ho fatto per ottenere un sistema del primo ordine, l'errore a regime, a fronte di un ingresso costante quale il gradino, è nullo e, nel contesto della regolazione industriale, proprio l'azione integrale I garantisce errore nullo a fronte di segnali di riferimento e disturbi additivi costanti. Inoltre la regolazione I è utilizzata quando è necessaria un'azione integrale per il soddisfacimento dei requisiti sull'errore a transitorio esaurito, ma non si richiedono prestazioni elevate in termini di velocità di risposta del sistema.

In effetti potrebbe già andare così ma accostandogli un'azione proporzionale P si introdurrebbe uno zero nella f.d.t. del sistema intero tale da avere una banda passante più ampia rispetto a quella I e quindi maggiore prontezza del sistema. Io credo proprio che si pervenga esattamente a questo compromesso nel caso del PLL, sempre considerando le semplificazioni che ho fatto e l'ipotesi di operare in zona di linearità del comparatore.

Effettivamente la domanda è più che lecita perché, per via delle semplificazioni che ho fatto per ottenere un sistema del primo ordine, l'errore a regime, a fronte di un ingresso costante quale il gradino, è nullo e, nel contesto della regolazione industriale, proprio l'azione integrale I garantisce errore nullo a fronte di segnali di riferimento e disturbi additivi costanti. Inoltre la regolazione I è utilizzata quando è necessaria un'azione integrale per il soddisfacimento dei requisiti sull'errore a transitorio esaurito, ma non si richiedono prestazioni elevate in termini di velocità di risposta del sistema.

In effetti potrebbe già andare così ma accostandogli un'azione proporzionale P si introdurrebbe uno zero nella f.d.t. del sistema intero tale da avere una banda passante più ampia rispetto a quella I e quindi maggiore prontezza del sistema. Io credo proprio che si pervenga esattamente a questo compromesso nel caso del PLL, sempre considerando le semplificazioni che ho fatto e l'ipotesi di operare in zona di linearità del comparatore.

"Lo scienziato descrive ciò che esiste, l'ingegnere crea ciò che non era mai stato."

(T. von Kármán)

(T. von Kármán)

0

voti

Ti ringrazio  jordan20 per la risposta.

jordan20 per la risposta.

Questa del PLL è stata anche occasione per me per ripassare quel poco di elettronica che ho studiato nel paleolitico superiore.

Questa del PLL è stata anche occasione per me per ripassare quel poco di elettronica che ho studiato nel paleolitico superiore.

"La follia sta nel fare sempre la stessa cosa aspettandosi risultati diversi".

"Parla soltanto quando sei sicuro che quello che dirai è più bello del silenzio".

Rispondere è cortesia, ma lasciare l'ultima parola ai cretini è arte.

"Parla soltanto quando sei sicuro che quello che dirai è più bello del silenzio".

Rispondere è cortesia, ma lasciare l'ultima parola ai cretini è arte.

-

TardoFreak

TardoFreak

73,9k 8 12 13 - -EY Legend-

- Messaggi: 15754

- Iscritto il: 16 dic 2009, 11:10

- Località: Torino - 3° pianeta del Sistema Solare

0

voti

Ok ho capito il funzionamento, grazie per le risposte. Lo schema che avevo in mente è il seguente:

Adesso avrei un altro dubbio per quanto riguarda il PLL digitale considerando questo schema:

Praticamente il compito svolto è lo stesso, ma è diverso il funzionamento. In questo caso il segnale d'ingresso è campionato e comparato con il segnale ricostruito in uscita. Viene prodotto quindi un errore di fase digitale proporzionale alla differenza di fase dei due segnali. Questo errore verrà filtrato e poi integrato ed entrerà nel circuito digitale DDS, che verrà forzato a produrre il quale produce in uscita un codice digitale che rappresenta una frequenza maggiore o minore dell'errore di fase, il codice digitale in uscita verrà campionato e confrontato nuovamente con l'ingresso e a regime l'errore tenderà ad annullarsi. Non ho capito alcune cose, l'integratore svolge la stessa funzione che aveva l'amplificatore nell'analogico? Il DDS cambia il valore della frequenza d'ingresso avanzando di un certo incremento essendo forzato dal segnale in ingresso?

Adesso avrei un altro dubbio per quanto riguarda il PLL digitale considerando questo schema:

Praticamente il compito svolto è lo stesso, ma è diverso il funzionamento. In questo caso il segnale d'ingresso è campionato e comparato con il segnale ricostruito in uscita. Viene prodotto quindi un errore di fase digitale proporzionale alla differenza di fase dei due segnali. Questo errore verrà filtrato e poi integrato ed entrerà nel circuito digitale DDS, che verrà forzato a produrre il quale produce in uscita un codice digitale che rappresenta una frequenza maggiore o minore dell'errore di fase, il codice digitale in uscita verrà campionato e confrontato nuovamente con l'ingresso e a regime l'errore tenderà ad annullarsi. Non ho capito alcune cose, l'integratore svolge la stessa funzione che aveva l'amplificatore nell'analogico? Il DDS cambia il valore della frequenza d'ingresso avanzando di un certo incremento essendo forzato dal segnale in ingresso?

0

voti

ireon ha scritto:l'integratore svolge la stessa funzione che aveva l'amplificatore nell'analogico?

No, svolge la stessa azione del circuito integratore che si trova dentro il VCO e che ti ho spiegato sopra.

ireon ha scritto:Il DDS cambia il valore della frequenza d'ingresso avanzando di un certo incremento essendo forzato dal segnale in ingresso?

Dipende a cosa ti riferisci per incremento. Il PLL digitale può manipolare singoli bit o parole intere, dipende dal modello integrato implementato.

Curiosità: dove li stai studiando?

"Lo scienziato descrive ciò che esiste, l'ingegnere crea ciò che non era mai stato."

(T. von Kármán)

(T. von Kármán)

0

voti

Ok il funzionamento generale del PLL analogico l'ho capito. Ora avrei dei dubbi sul funzionamento del PLL digitale. Allora premetto che ho gli appunti sul quaderno e sto cercando di dargli un senso con scarsi risultati  Ho trovato qualche informazione sul DDS a questo link http://it.wikipedia.org/wiki/Direct_Digital_Synthesis

Ho trovato qualche informazione sul DDS a questo link http://it.wikipedia.org/wiki/Direct_Digital_Synthesis

Lo schema che ho sul quaderno è quello che ho postato sopra. Il funzionamento generale è lo stesso, però questa volta in uscita e in ingresso avrò un segnale campionato e non un segnale analogico. Essendo il segnale ricostruito attraverso i suoi campioni il primo blocco misura lo sfasamento confrontando la differenza dei campioni tra ingresso e uscita. A questo punto i campioni vengono filtrati e arrivano al DDS, che viene fatto avanzare di un certo incremento, ad esempio supponiamo che viene incrementato di 3, a questo punto il bit meno significativo LSB si sposta di tre posizioni aumentando ad esempio il valore della frequenza, che si avvicina al valore della frequenza d'ingresso. A questo punto il codice digitale in uscita dal DDS che mi rappresenta il nuovo valore della frequenza in termini di bit viene convertito dal DAC e riportato in ingresso per essere nuovamente confrontato. Come nel PLL a regime l'errore tenderà a 0. A grandi linee questo è quello che ho capito, quello che devo sapere è il funzionamento dello schemo a blocchi generale, senza entrare nel dettaglio utilizzando formule o altro.

Lo schema che ho sul quaderno è quello che ho postato sopra. Il funzionamento generale è lo stesso, però questa volta in uscita e in ingresso avrò un segnale campionato e non un segnale analogico. Essendo il segnale ricostruito attraverso i suoi campioni il primo blocco misura lo sfasamento confrontando la differenza dei campioni tra ingresso e uscita. A questo punto i campioni vengono filtrati e arrivano al DDS, che viene fatto avanzare di un certo incremento, ad esempio supponiamo che viene incrementato di 3, a questo punto il bit meno significativo LSB si sposta di tre posizioni aumentando ad esempio il valore della frequenza, che si avvicina al valore della frequenza d'ingresso. A questo punto il codice digitale in uscita dal DDS che mi rappresenta il nuovo valore della frequenza in termini di bit viene convertito dal DAC e riportato in ingresso per essere nuovamente confrontato. Come nel PLL a regime l'errore tenderà a 0. A grandi linee questo è quello che ho capito, quello che devo sapere è il funzionamento dello schemo a blocchi generale, senza entrare nel dettaglio utilizzando formule o altro.

12 messaggi

• Pagina 1 di 2 • 1, 2

Chi c’è in linea

Visitano il forum: Nessuno e 43 ospiti

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)