Che ne dite di progettare la stessa macchina in sincrono?

Scelgo di progettare una macchina di Moore.

Diagramma a stati:

In questo diagramma ho riportato in rosso lo stato e, subito dopo la barra, la relativa uscita, che andrà collegata al LED.

Lo stato del pulsante è stato indicato con P. P=0 significa "pulsante premuto".

Sono presenti due stati trappola, indicati con la scritta "TRAP STATE". Servono per fare in modo che, quando viene premuto il pulsante P, la macchina non si porti in uno stato stabile finché il tasto non viene rilasciato. Questo serve per fare in modo che, premendo il tasto, la macchina non commuti di continuo tra lo stato LED ACCESO/LED SPENTO ma si fermi finché il tasto non viene rilasciato.

Il "fulmine" con la scritta RESET indica lo stato nel quale viene forzata la macchina all'accensione.

Noterete che ho forzato la macchina a portarsi, all'accensione, in un TRAP STATE. Quando ci sono dei pulsanti conviene sempre forzare la macchina in un TRAP STATE, perché il condensatore che viene utilizzato per fare l'antirimbalzo dei pulsanti, all'accensione, risulta scarico, quindi la macchina è portata a credere che il pulsante sia premuto e, quindi, commuta l'uscita. Inoltre non è possibile fare previsioni sulla durata di questo evento perché non si otterrebbe un risultato affidabile. Meglio portare la macchina in un TRAP STATE che la condurrà, quando P verrà rilasciato, allo stato "LED SPENTO". Fino a che il condensatore è carico rimarrà nel TRAP STATE, dopodichè si porterà nello stato "LED SPENTO".

Il condensatore in questione fa parte del circuito antirimbalzo del pulsante, comunque necessario, perché, altrimenti, la macchina sarebbe portata a credere che l'utente stia premendo ripetutamente il pulsante e, quindi, farebbe più accensioni/spegnimenti con un singolo azionamento.

Per fare un circuito antirimbalzo completamente digitale sarebbe necessario inserire un contatore che conteggi un tempo di "blanking". Questa è la soluzione che viene solitamente impiegata quando si implementa la FSM su logica programmabile.

La numerazione scelta, per gli stati, è quella che minimizza la logica circuitale.

Facciamo quindi la mappa degli stati, ricavandola dal diagramma a stati:

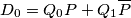

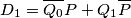

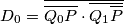

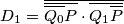

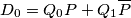

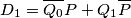

Le funzioni logiche per

e

sono quindi:

Per l'uscita Y (il LED) è possibile notare che

Scelgo di implementare la rete utilizzando solo porte NAND (e sceglierò un

74HCT132, in modo da poterle utilizzare anche per fare l'oscillatore e l'antirimbalzo per il tasto).

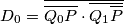

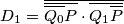

Riscrivo quindi le funzioni logiche in modo da usare solo NAND:

Per quanto riguarda il tasto P, dato che è disponibile un FF in più, dopo averlo ripulito dai rimbalzi, scelgo di renderlo sincrono, in modo da non avere un bit asincrono nella rete, che potrebbe creare problemi di vario tipo. In questo modo risparmio anche una NAND perché all'uscita del FF avrò sia P che P negato.

Per quanto riguarda l'oscillatore, direi che anche una frequenza ridicola, pari per esempio a 10kHz, sia più che sufficiente.

Facendo i calcoli per delle porte di tipo HCT, la frequenza ottenuta da un oscillatore a singola porta NAND è

.

Scegliendo un condensatore di capacità pari a 10nF (la capacità di ingresso della porta è dell'ordine delle decine di pF, quindi 10nF va bene) devo impiegare quindi un resistore di resistenza pari a

circa. Con questi valori ottengo f=9259Hz circa. Direi che va benissimo.

La stessa formula mi permette anche di progettare il circuito antirimbalzo, scrivendola come:

.

Ipotizzando un tempo di rimbalzo per il tasto di 30ms ottengo

e

. In serie al pulsante metterò una resistenza pari a

, in modo da contenere la corrente di chiusura del tasto e garantire che il condensatore non si scarichi di colpo, cosa che potrebbe dare qualche commutazione non desiderata.

Non resta che mettere tutte le cose insieme e disegnare quindi lo schema elettrico:

Ecco come viene progettata una macchina a stati (FSM) a livello professionale.

Chiaramente la complicazione della logica, rispetto a una macchina asincrona, ne risente.

Per la verità, in questo caso, nemmeno più di tanto, avendo impiegato solo tre integrati.

Macchine sincrone più complesse vengono oggi implementate su FPGA o microcontrollori, dove i problemi relativi al contenimento del numero di FF o di porte logiche sono infinitamente meno sentiti.

Con questo è tutto.

Pietro.

PS: YAHHHWM... maledetta insonnia...è colpa sua se mi metto a scrivere 'ste robe

![]() carloc,

carloc, ![]() g.schgor,

g.schgor, ![]() BrunoValente,

BrunoValente, ![]() IsidoroKZ

IsidoroKZ

e

e  sono quindi:

sono quindi:

.

. circa. Con questi valori ottengo f=9259Hz circa. Direi che va benissimo.

circa. Con questi valori ottengo f=9259Hz circa. Direi che va benissimo. .

. e

e  . In serie al pulsante metterò una resistenza pari a

. In serie al pulsante metterò una resistenza pari a  , in modo da contenere la corrente di chiusura del tasto e garantire che il condensatore non si scarichi di colpo, cosa che potrebbe dare qualche commutazione non desiderata.

, in modo da contenere la corrente di chiusura del tasto e garantire che il condensatore non si scarichi di colpo, cosa che potrebbe dare qualche commutazione non desiderata.