buonasera a tutto il forum,

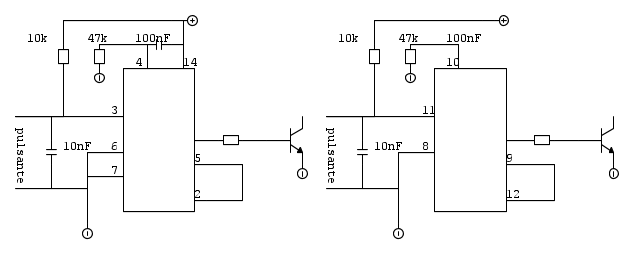

ho trovato questo schema che fa funzionare un rele' da bistabile con un solo pulsante

io vorrei evitare che si possano trovare le due uscite contemporaneamente a livello 1

si puo' fare senza troppe complicazioni?

una cosa che non riesco a capire : al momento che alimento il circuito sono entrambi a livello 0 o sbaglio ?

grazie mille e buona cena a tutti

evitare 2 uscite alte insieme

Moderatori: ![]() carloc,

carloc, ![]() g.schgor,

g.schgor, ![]() BrunoValente,

BrunoValente, ![]() IsidoroKZ

IsidoroKZ

15 messaggi

• Pagina 1 di 2 • 1, 2

0

voti

Quali sono le due uscite?

Sarebbe anche gentile se tu rifacessi lo schemino in FidoCAD, come da regolamento. È molto piú semplice per chi legge lo schema se invece di un rettangolo con la scritta 4013 usi i simboli logici di un Flip-Flop.

Ciao Boiler

Sarebbe anche gentile se tu rifacessi lo schemino in FidoCAD, come da regolamento. È molto piú semplice per chi legge lo schema se invece di un rettangolo con la scritta 4013 usi i simboli logici di un Flip-Flop.

Ciao Boiler

0

voti

scusa credevo di averlo scritto , ho 2 circuiti uguali (il 4013) ha 2 flip flop

come si fa a installare fidocad su ubuntu? c'e' una guida?

come si fa a installare fidocad su ubuntu? c'e' una guida?

-

danielealfa

danielealfa

243 2 4 7 - Expert

- Messaggi: 1313

- Iscritto il: 27 mag 2009, 22:51

1

voti

danielealfa ha scritto:scusa credevo di averlo scritto , ho 2 circuiti uguali (il 4013) ha 2 flip flop

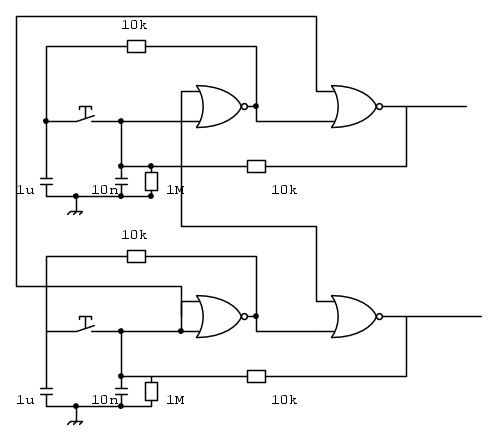

Metti una porta NOR (4001) in uscita al canale secondario (quello che viene inibito se tutte e due le uscite vanno a 1). La porta NOR dà però in uscita 1 se e soltanto se ambo gli ingressi sono 0, quindi il canale secondario devi prelevarlo da Q-negato e non da Q.

Per dovere di cronaca, il circuito è una ciofeca

come si fa a installare fidocad su ubuntu? c'e' una guida?

È Java, non va installato, da console, java <nome-del-programma>

Ciao Boiler

0

voti

non ho il simbolo del flip flop ...ho messi i 2 circuiti anche se sono nello stesso integrato

-

danielealfa

danielealfa

243 2 4 7 - Expert

- Messaggi: 1313

- Iscritto il: 27 mag 2009, 22:51

1

voti

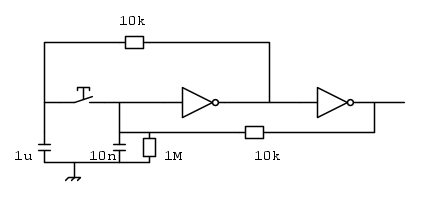

Ripeto, il circuito è una ciofeca. Il debouncing è probabilmente stato riciclato (senza capirne il funzionamento) da un circuito con un flip-flop a fianco attivo negativo. Con questi componenti siamo oltre i 100 microsecondi di raise-time. Il 4013 specifica un massimo di 10 microsecondi. Prima o poi l'insorgere di metastabilità è una garanzia.

Non parliamo poi di quella tristezza di power-on-reset.

Se permetti...

All'accensione il condensatore da 10 nF è scarico a causa del resistore da 1M in parallelo. L'ingresso del primo gate è quindi basso. Questo forza l'uscita allo stesso stato. L'unica possibilità che abbiamo di lasciare questo stato è caricare il condensatore da 10 nF, ma questo è saldamente tenuto a 0 V attraverso il resistore da 10k. Può succedere che il condensatore venga caricato durante il transiente di accensione? Se i due gates sono nello stesso package si accendono contemporaneamente e se siamo sfigati c'è un intervallo pari alla differenza dei propagation-delays durante il quale l'uscita può essere alta. Se questo intervallo eccede il tempo necessario a caricare 10 nF attraverso 10k fino al threshold del gate, allora sì, abbiamo un problema. Ma siamo due ordini di grandezza sotto. Il power-on reset è quantomento granitico.

La commutazione avviene (ovviamente) azionando il tasto. Nel frattempo il condensatore da 1 μF si è caricato al potenziale presente al nodo tra i due gates (che è alto se l'uscita è bassa e viceversa). Premento il pulsante mettiamo in parallelo i condensatori. Uno (da 10 nF) cerca di tenere lo stato attuale, l'altro (da 1 μF) cerca di commutarlo. Credo sia chiaro chi vince

Il potenziale vincitore (ovviamente quello che era presente tra i due gates) si trova ora all'ingresso del primo gate, che commuta e porta l'uscita (attraverso il secondo gate) all'altro stato.

E ora il condensatore grosso e grasso può essere caricato al nuovo potenziale.

Ancora una parola sulla stabilità di questo circuito: l'impedenza d'ingresso si un gate CMOS è molto elevata, basta un nulla e commuta. I 10k di feedback basterebbero nel 95% dei casi a tenere lo stato ben determinato ed evitare commutazioni spurie, nel restante 5% dei casi interviene il condensatore del power-on reset a fare da blando filtro.

Questo circuito sostituisce il tuo flip-flop.

Compito a casa: usando una porte NOR si possono simulare tutti gli altri gate. Ridisegna il circuito usando porte NOR e introducendo la modifica che ti ho detto per evitare la presenza di due uscite contemporaneamente attive.

Ciao Boiler

Non parliamo poi di quella tristezza di power-on-reset.

Se permetti...

All'accensione il condensatore da 10 nF è scarico a causa del resistore da 1M in parallelo. L'ingresso del primo gate è quindi basso. Questo forza l'uscita allo stesso stato. L'unica possibilità che abbiamo di lasciare questo stato è caricare il condensatore da 10 nF, ma questo è saldamente tenuto a 0 V attraverso il resistore da 10k. Può succedere che il condensatore venga caricato durante il transiente di accensione? Se i due gates sono nello stesso package si accendono contemporaneamente e se siamo sfigati c'è un intervallo pari alla differenza dei propagation-delays durante il quale l'uscita può essere alta. Se questo intervallo eccede il tempo necessario a caricare 10 nF attraverso 10k fino al threshold del gate, allora sì, abbiamo un problema. Ma siamo due ordini di grandezza sotto. Il power-on reset è quantomento granitico.

La commutazione avviene (ovviamente) azionando il tasto. Nel frattempo il condensatore da 1 μF si è caricato al potenziale presente al nodo tra i due gates (che è alto se l'uscita è bassa e viceversa). Premento il pulsante mettiamo in parallelo i condensatori. Uno (da 10 nF) cerca di tenere lo stato attuale, l'altro (da 1 μF) cerca di commutarlo. Credo sia chiaro chi vince

Il potenziale vincitore (ovviamente quello che era presente tra i due gates) si trova ora all'ingresso del primo gate, che commuta e porta l'uscita (attraverso il secondo gate) all'altro stato.

E ora il condensatore grosso e grasso può essere caricato al nuovo potenziale.

Ancora una parola sulla stabilità di questo circuito: l'impedenza d'ingresso si un gate CMOS è molto elevata, basta un nulla e commuta. I 10k di feedback basterebbero nel 95% dei casi a tenere lo stato ben determinato ed evitare commutazioni spurie, nel restante 5% dei casi interviene il condensatore del power-on reset a fare da blando filtro.

Questo circuito sostituisce il tuo flip-flop.

Compito a casa: usando una porte NOR si possono simulare tutti gli altri gate. Ridisegna il circuito usando porte NOR e introducendo la modifica che ti ho detto per evitare la presenza di due uscite contemporaneamente attive.

Ciao Boiler

0

voti

ok, grazie per il prezioso indizio, pero' io ho in problema , se si puoi definire cosi,

ho un polo dei pulsanti connesso a gnd, o eventualmente a vcc 12 volt,

mi viene un po' problematico, a meno che al posto del pulsante possa usare un transistor

ia quale base e' comandata dal pulsante, cosi 'e' fattibile?

ho un polo dei pulsanti connesso a gnd, o eventualmente a vcc 12 volt,

mi viene un po' problematico, a meno che al posto del pulsante possa usare un transistor

ia quale base e' comandata dal pulsante, cosi 'e' fattibile?

-

danielealfa

danielealfa

243 2 4 7 - Expert

- Messaggi: 1313

- Iscritto il: 27 mag 2009, 22:51

0

voti

ciao , grazie della tua spiegazione cosi approfondita, ho pensato a questa soluzione, spero che

sia giusta, almeno e succo della mia testa..

sia giusta, almeno e succo della mia testa..

-

danielealfa

danielealfa

243 2 4 7 - Expert

- Messaggi: 1313

- Iscritto il: 27 mag 2009, 22:51

15 messaggi

• Pagina 1 di 2 • 1, 2

Chi c’è in linea

Visitano il forum: Nessuno e 101 ospiti

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)