Vorrei un confronto con qualcuno più preparato(sicuramente) di me. In ogni caso vi saluto e vi auguro una buona giornata

Moderatori: ![]() carloc,

carloc, ![]() g.schgor,

g.schgor, ![]() BrunoValente,

BrunoValente, ![]() IsidoroKZ

IsidoroKZ

è il ritardo di propagazione

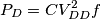

è il ritardo di propagazione è la potenza media dissipata dalla porta CMOS, la quale ha come maggior contributo la potenza necessaria a caricare-scaricare la capacità di carico C della porta, quindi la potenza dinamica, che è data dalla:

è la potenza media dissipata dalla porta CMOS, la quale ha come maggior contributo la potenza necessaria a caricare-scaricare la capacità di carico C della porta, quindi la potenza dinamica, che è data dalla:

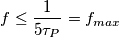

è la frequenza di commutazione.

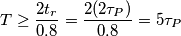

è la frequenza di commutazione. è legata alla durata T dell' intero ciclo carica-scarica della capacità di carico C, dalla relazione:

è legata alla durata T dell' intero ciclo carica-scarica della capacità di carico C, dalla relazione:

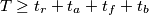

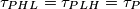

è il tempo di salita (rise time) e

è il tempo di salita (rise time) e  quello di discesa (fall time).

quello di discesa (fall time). e

e  occupano circa l' 80 % del periodo T;

occupano circa l' 80 % del periodo T; e

e  , e ricordando che i tempi di salita e discesa sono all' incirca pari al doppio dei corrispondenti tempi di propagazione, cioè:

, e ricordando che i tempi di salita e discesa sono all' incirca pari al doppio dei corrispondenti tempi di propagazione, cioè: e

e

.

.

):

):

Cesc99 ha scritto:...qualche altro pdf che dice che è il doppio del tempo di propagazione,come precedentemente scritto nel virgolettato.

?

?Cesc99 ha scritto:Non so chi dei due seguire,non voglio screditare ciò da te scritto,però vorrei sentire anche qualche altro parere..

Nel caso CMOS si può ricavare dalla formula della potenza, notando che la massima frequenza di funzionamento dell’inverter è pari al doppio del tempo di propagazione.

, il che ha senso.

, il che ha senso. considera solo la potenza dinamica

considera solo la potenza dinamica  che serve a caricare-scaricare la capacità di carico C, tralasciando sia la potenza statica, sia la parte di potenza dinamica dovuta al "direct path" (percorso diretto) che si ha in quel brevissimo lasso di tempo, durante la fase di commutazione, in cui sia l' n-MOS che il p-MOS sono in conduzione (precisamente in saturazione) instaurando un percorso diretto, cioè cortocircuitando, tra massa e alimentazione.

che serve a caricare-scaricare la capacità di carico C, tralasciando sia la potenza statica, sia la parte di potenza dinamica dovuta al "direct path" (percorso diretto) che si ha in quel brevissimo lasso di tempo, durante la fase di commutazione, in cui sia l' n-MOS che il p-MOS sono in conduzione (precisamente in saturazione) instaurando un percorso diretto, cioè cortocircuitando, tra massa e alimentazione.Cesc99 ha scritto:Penso che andare a ricevimento dal prof,sia l'unica via percorribile per ottenere un riscontro..

, e forse anche un po' troppo ottimista.

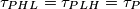

, e forse anche un po' troppo ottimista.  il ritardo di propagazione per la transizione H-L, e con

il ritardo di propagazione per la transizione H-L, e con  il ritardo di propagazione per la transizione L-H.

il ritardo di propagazione per la transizione L-H. , si può vedere che scrivere

, si può vedere che scrivere  , significa assumere che l' intero periodo T sia approssimabile con

, significa assumere che l' intero periodo T sia approssimabile con  (dove, per semplicità, si assume che

(dove, per semplicità, si assume che  ).

). , visto che sia

, visto che sia  che

che  sono circa uguali al doppio del tempo di propagazione.

sono circa uguali al doppio del tempo di propagazione.Visitano il forum: Nessuno e 93 ospiti